Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

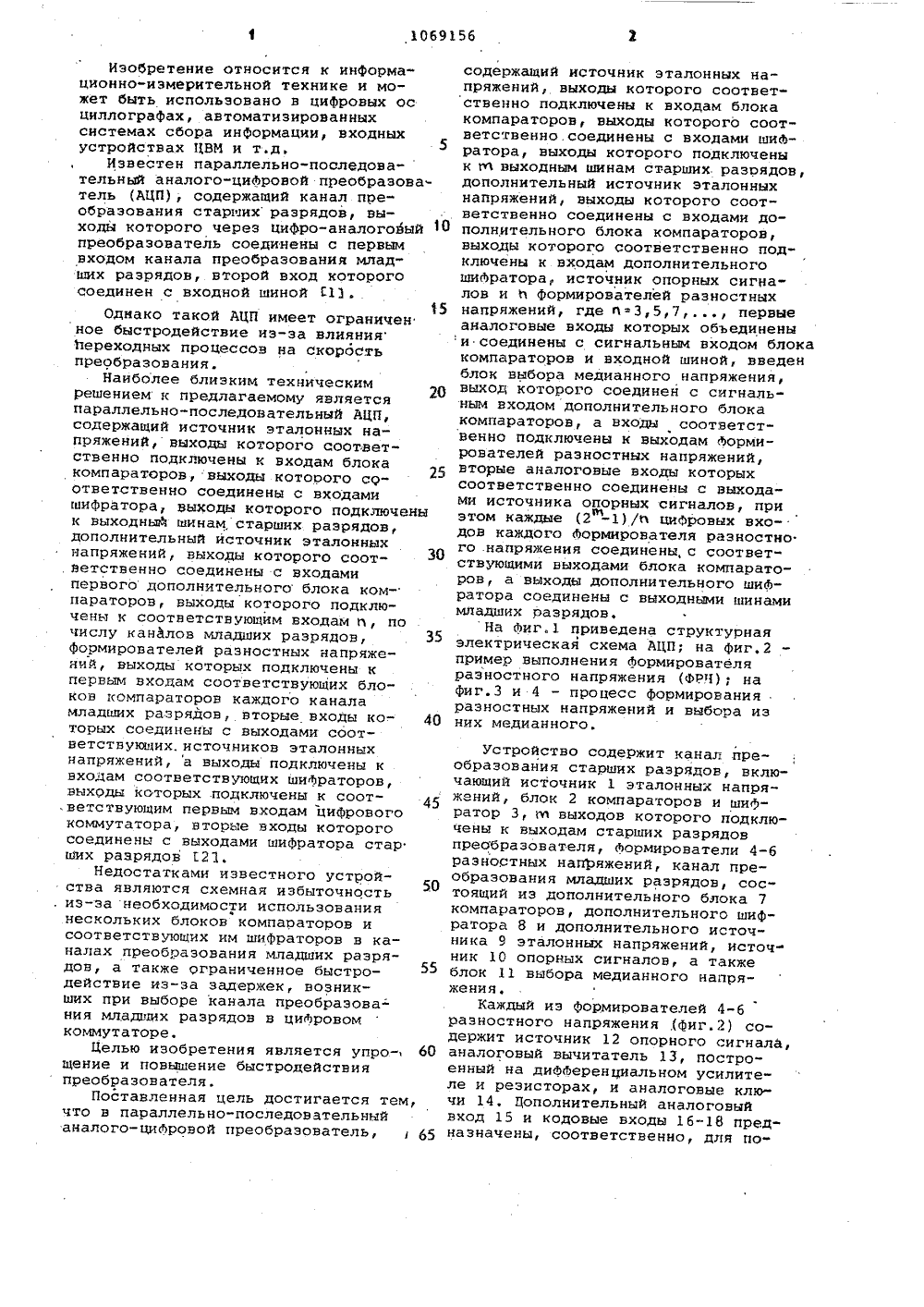

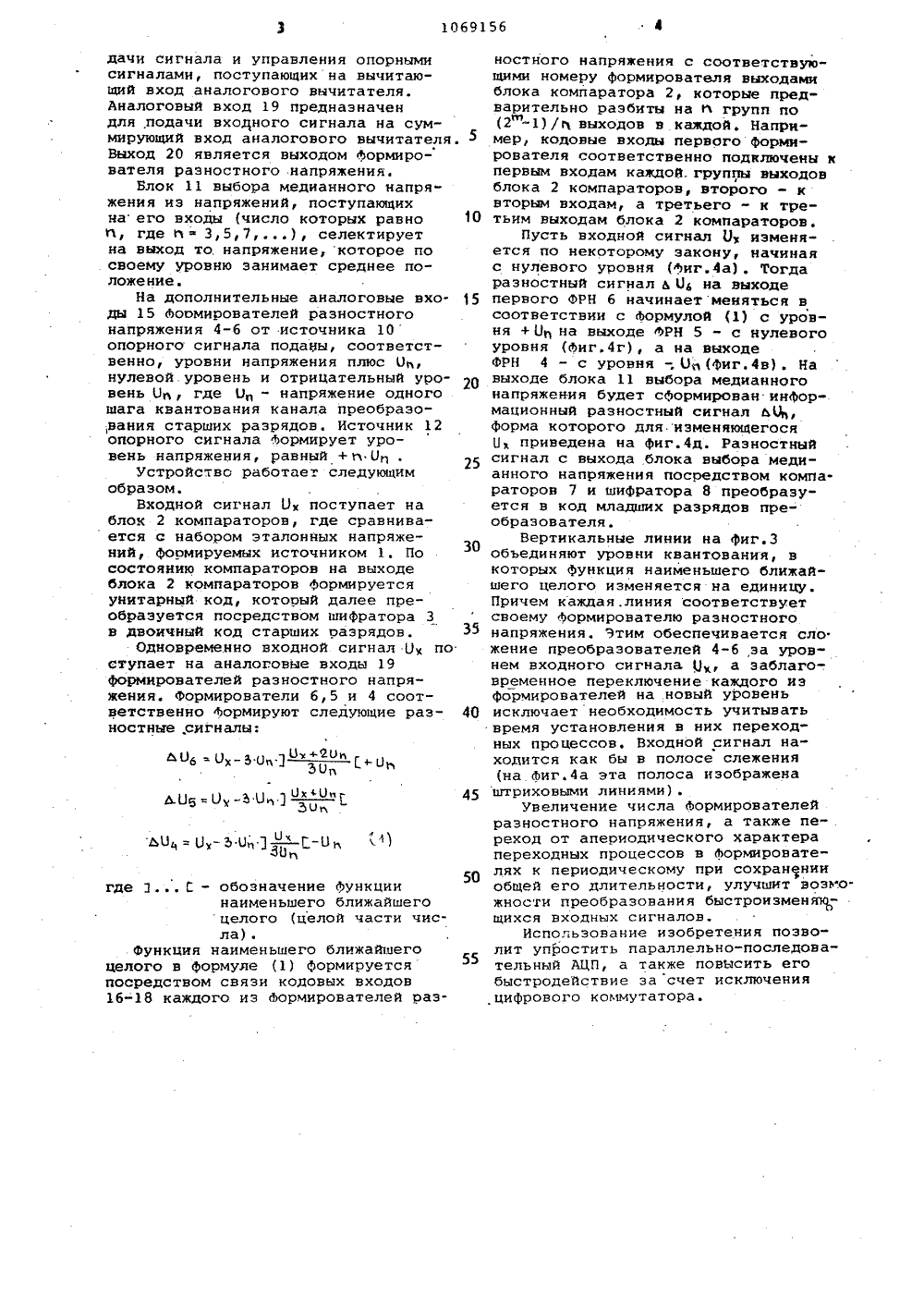

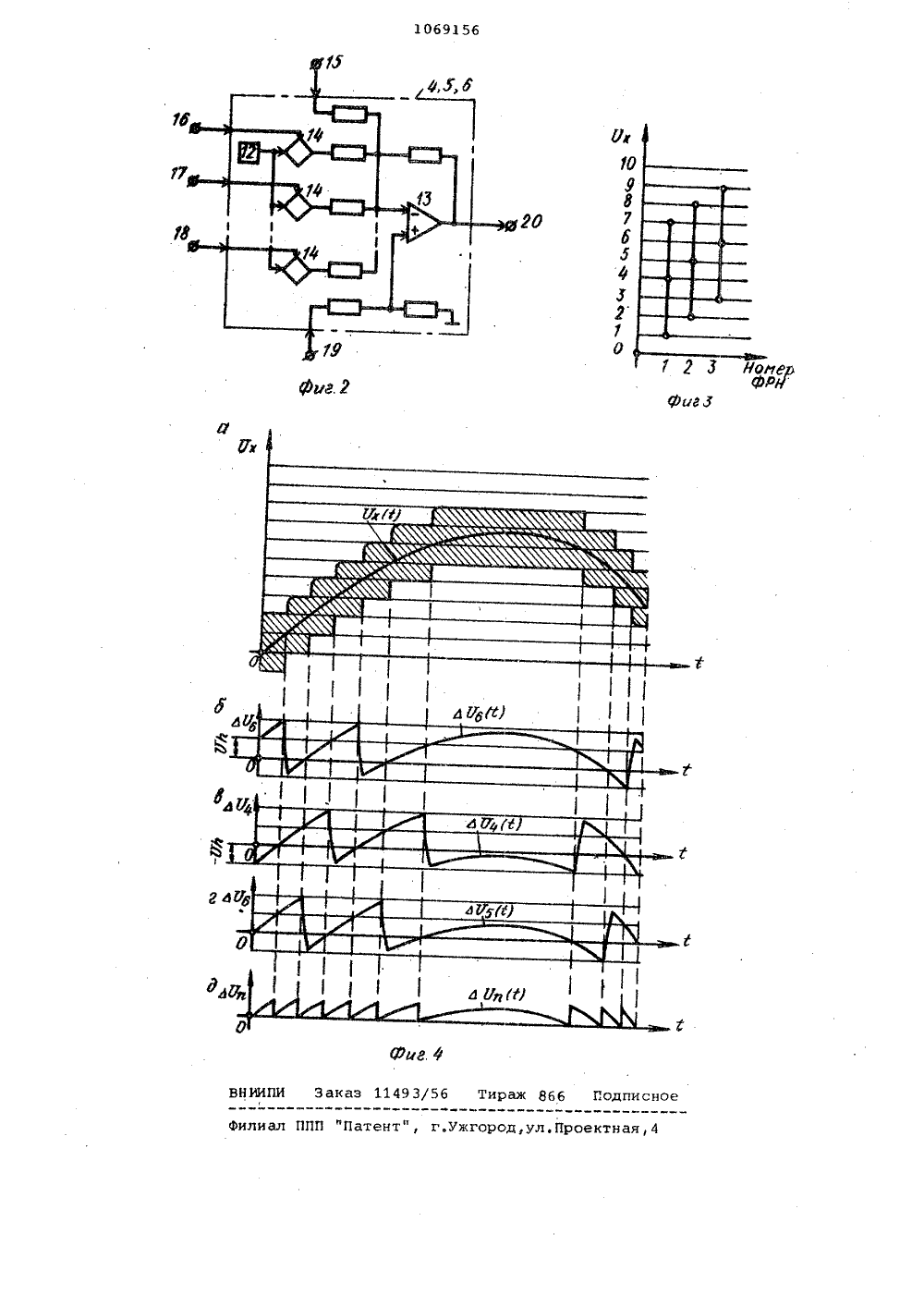

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСН СПУБЛИК ПИСА Е РЕТ Н АВТОРСКОМУ ЕТЕЛ У(46) 23.01.84. Бюл (72) С.А.Волощенко (53) 621.325(088,8 (56), 1. Гитис Э,И. инФормации для элек устройств. М., Эн 319, рис. 7-11.2. Авторское сви 9 799131, кл. Ч 03 23.01.81 (прототип 3.П.Петрен Преобратронныхергия ователнциФровых с,316 тво ССС5,детел К 13/ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО делАм изОБРетений и ОткРытий(54)(57) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ,содержащий источник эталонных напряжений, выходы которого соответственно подключены к входам блока компараторов, выходы которого соответственно соединены с входамишиФратора, выходы которого подключе-,ны к выходным шинам старших разрядов, дополнительный источникэталонных напряжений, выходы которого соответственно соединены с входами дополнительного блока компараторов, выходы которого соответственно подключены к входам дополнительного шиФратора, источник опорных сигналов и а формирователей раз" ностных напряжений, где п 3,5,7 первые аналоговые входы которых объединены и соединены с сигнальным входом блока компараторов и входной шиной, о т л и ч. а ю щ и йс я .тем, что, с целью упрОщения и повышения быстродействия преобразователя, в него введен блок выбора медианного напряжения, выход которого соединен с сигнальным входом дополнительного блока компараторов, а входы соответственно подключены к выходам Формирователей разностных напряжений, вторые ана- Я логовые входы которых соответственно соединены с выходами источ" ника опорных сигналов, при этом каждые (2 -1)/ цифровых входов каж- С дого Формирователя разностного напряжения соединены с соответствующими выходами блока компараторов, а выходы дополнительного шиФратора соединены с выходными шинами младших разрядов.Изобретение относится к информационно"измерительной технике и может быть использовано в цифровых осциллографах, автоматизированныхсистемах сбора информации, входныхустройствах ЦВМ и т.д,Известен параллельно-последовательный аналого-цифровой преобразователь (АЦП), содержащий канал преобразования старших разрядов, выходы которого через цифро-аналоговыйпреобразователь соединены с первымвходом канала преобразования младших разрядон, второй вход которогосоединен с входной шиной Г 13,15Однако такой АЦП имеет ограниченное быстродействие из-за влиянияпереходных процессов на скоростьпреобразования.Наиболее близким техническимрешением к предлагаемому являетсяпараллельно-последовательный АЦП,содержащий источник эталонных напряжений, выходы которого соответственно подключены к входам блокакомпараторов, выходы котооого со"ответственно соединены с входамишифратора, выходы которого подключенык ныходньЮ шинам, старших разрядов,дополнительный источник эталонныхнапряжений, выходы которого соот. ветственно соединены с входамипервого дополнительного блока компараторон, выходы которого подключены к соотнетатнующим входам и, почислу каналов младших разрядов, . 35Формирователей раэностных напряжений, выходы которых подключены кпервым входам соответствующих блоков компараторов каждого каналамладших разрядов, вторые входы ко Оторых соединены с выходами соответстнующих,источников эталонныхнапряжений, а выходы подключены квходам соответствующих шифраторов,выходы которых .подключены к соот.ветствующим первым входам цифровогокоммутатора, вторые входы которогосоединены с выходами шифратора старших разрядов 121.Недостатками известного устройства являются схемная избыточность, из-за необходимости использованиянескольких блоков компараторов исоответствующих им шифраторов н каналах преобразования младших разрядов, а также ограниченное быстродействие из-за задержек, нозникших при выборе канала преобразова-ния младших разрядов в цифровомкоммутаторе.Целью изобретения является упрощение и повышение быстродейстнияпреобразователя.Поставленная цель достигается тем,что в параллельно-последовательныйаналого-цифровой преобразователь,65 содержащий источник эталонных напряжений, выходы которого соответственно подключены к входам блокакомпараторов, выходы которого соответственно.соединены с входами шифратора, выходы которого подключенык м выходным шинам старших. разрядов,дополнительный источник эталонныхнапряжений, ныходы которого соответственно соединены с входами дополнительного блока компараторов,выходы которого соответственно подключены к входам дополнительногошифратора источник опорных сигналон и и формирователей разностныхнапряжений, где п 3,5,7.первыеаналоговые входы которых объединеныи соединены с сигнальным входом блокакомпараторов и входной шиной, введенблок выбора медианного напряжения,выход которого соединен с сигнальным входом дополнительного блокакомпараторов, а входы соотнетственно подключены к выходам Формирователей разностных напряжений,вторые аналоговые входы которыхсоответственно соединены с выходами источника опорных сигналов, приэтом каждые (2 -1)/о цифровых вхойдов каждого Формирователя разностно.го .напряжения соединены, с соответствующими выходами блока компараторон, а выходы дополнительного шифратора соединены с выходными шинамимладших разрядов,На Фиг.1 приведена структурнаяэлектрическая схема АЦП," на Фиг,2пример выполнения Формирователяразностного напряжения (ФРа); нафиг.З и 4 - процесс формированияразностных напряжений и выбора изних медианного.Устройство содержит канал преобразования старших разрядов, включающий источник 1 эталонных напряжений, блок 2 компараторов и шифратор 3, м выходов которого подключены к выходам старших разрядов преобразователя, Формирователи 4-6 разнос:тных наФяжений канал преобразования младших раэрядон, состоящий из дополнительного блока 7 компараторов, дополнительного шифратора 8 и дополнительного источника 9 эталонных напряжений, источник 1 О опорных сигналон, а также блок 11 выбора медианного напряжения.Каждый иэ Формирователей 4-6 разностного напряжения ,(Фиг.2) содержит источник 12 опорного сигнала, аналоговый вычитатель 13, постро" енный на дифференциальном усилителе и резисторах, и аналоговые ключи 14. Цополнительный аналогоный вход 15 и кодовые входы 16-18 предназначены, соответственно, для по 1069156Об ОХ - Ъ Оп 1ОЗО,Ь.(.)6-О,-Ь О СЪ 45 ЬОц = О-Ъ 01 " -0350 где 1 С - обозначение функциинаименьшего ближайшегоцелого (целой части числа).Функция наименьшего ближайшего целого в Формуле (1) Формируется посредством связи кодовых входов 16-18 каждого иэ формирователей раэ 55 дачи сигнала и управления опорными сигналами, поступающих на вычитающий вход аналогового вычитателя. Аналоговый вход 19 предназначен для,подачи входного сигнала на суммирующий вход аналогового вычитателя. 5 Выход 20 является выходом Формирователя раэностного напряжения.Блок 11 выбора медианного напряжения иэ напряжений, поступающих наего входы (число которых равно 10 й, где й3,5,7,), селектирует на выход то. напряжение, которое по своему уровню занимает среднее положение.На дополнительные аналоговые вхо ды 15 Аоомирователей разностного напряжения 4-6 от источника 10 опорного сигнала поданы, соответственно, уровни напряжения плюс Оп, нулевой уровень и отрицательный уровень Оп, где 0 - напряжение одного шага квантования канала преобразо,вания старших разрядов. Источник 12 опорного сигнала формирует уровень напряжения, равный +Оп .25Устройство работает следующим образом.Входной сигнал 0 поступает на блок 2 компараторов, где сравнивается с набором эталонных напряжений, Фоомируемых источником 1. По состоянию компараторов на выходе блока 2 компараторов формируется унитарный код, который далее преобразуется посредством шифратора 3 в двоичный код старших разрядов. З 5Одновременно входной сигнал О по ступает на аналоговые входы 19 Формирователей разностного напряжения. Формирователи 6,5 и 4 соответственно формируют следующие раз ностные сигналы: ностного напряжения с соответствую"щими номеру формирователя выходамиблока компаратора 2, которые предварительно разбиты нагрупп по(2-1)/ выходов в каждой. Например, кодовые входы первого Формирователя соответственно подключены кпервым входам каждой. группы выходовблока 2 компараторов, второго - квторым входам, а третьего - к третьим выходам блока 2 компараторов.Пусть входной сигнал О изменяется по некоторому закону, начинаяс нулевого уровня (Фиг.4 а. Тогдаразностный сигнал ь О на выходепервого фРН 6 начинаетменяться всоответствии с формулой (1) с уровня + Оп на выходе ФРН 5 - с нулевогоуровня (фиг.4 г), а на выходеФРН 4 - с уровня в . 0,(фиг.4 в). Навыходе блока 11 выбора медианногонапряжения будет сформирован информационный разностный сигнал ЬО,форма которого для изменяющегосяЦ приведена на фиг.4 д. Разностныйсигнал с выхода блока выбора медианного напряжения посредством компа.раторов 7 и шифратора 8 преобразуется в код младших разрядов пре-образователя,Вертикальные линии на фиг.3объединяют уровни квантования, вкоторых Функция наименьшего ближайшего целого изменяется на единицу.Причем каждая. линия соответствуетсвоему формирователю разностногонапряжения. Этим обеспечивается сло.жение преобразователей 4-6,эа уровнем входного сигнала Ц, а заблаго-.временное переключение каждого изформирователей на новый уровеньисключает необходимость учитыватьвремя установления в них переходных процессов. Входной сигнал находится как бы в полосе слежения(на фиг,4 а эта полоса изображенаштриховыми линиями).Увеличение числа формирователейраэностного напряжения, а также переход от апериодического характерапереходных процессов в формирователях к периодическому при сохраненииобщей его длительности, улучшит воза.жности преобразования быстроизменяк;щихся входных сигналов.Использование изобретения позволит упростить параллельно-последовательный АЦП, а также повысить егобыстродействие за счет исключенияцифрового коммутатора.

СмотретьЗаявка

3425560, 01.02.1982

ПРЕДПРИЯТИЕ ПЯ В-2201

ВОЛОЩЕНКО СЕРГЕЙ АЛЕКСЕЕВИЧ, ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ

МПК / Метки

МПК: H03K 13/175

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 23.01.1984

Код ссылки

<a href="https://patents.su/4-1069156-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Преобразователь кода числа из системы остаточных классов в напряжение

Следующий патент: Аналого-цифровой преобразователь с цифровой коррекцией

Случайный патент: Устройство для направления и присучки нити при смене шпуль на мотальных машинах