Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

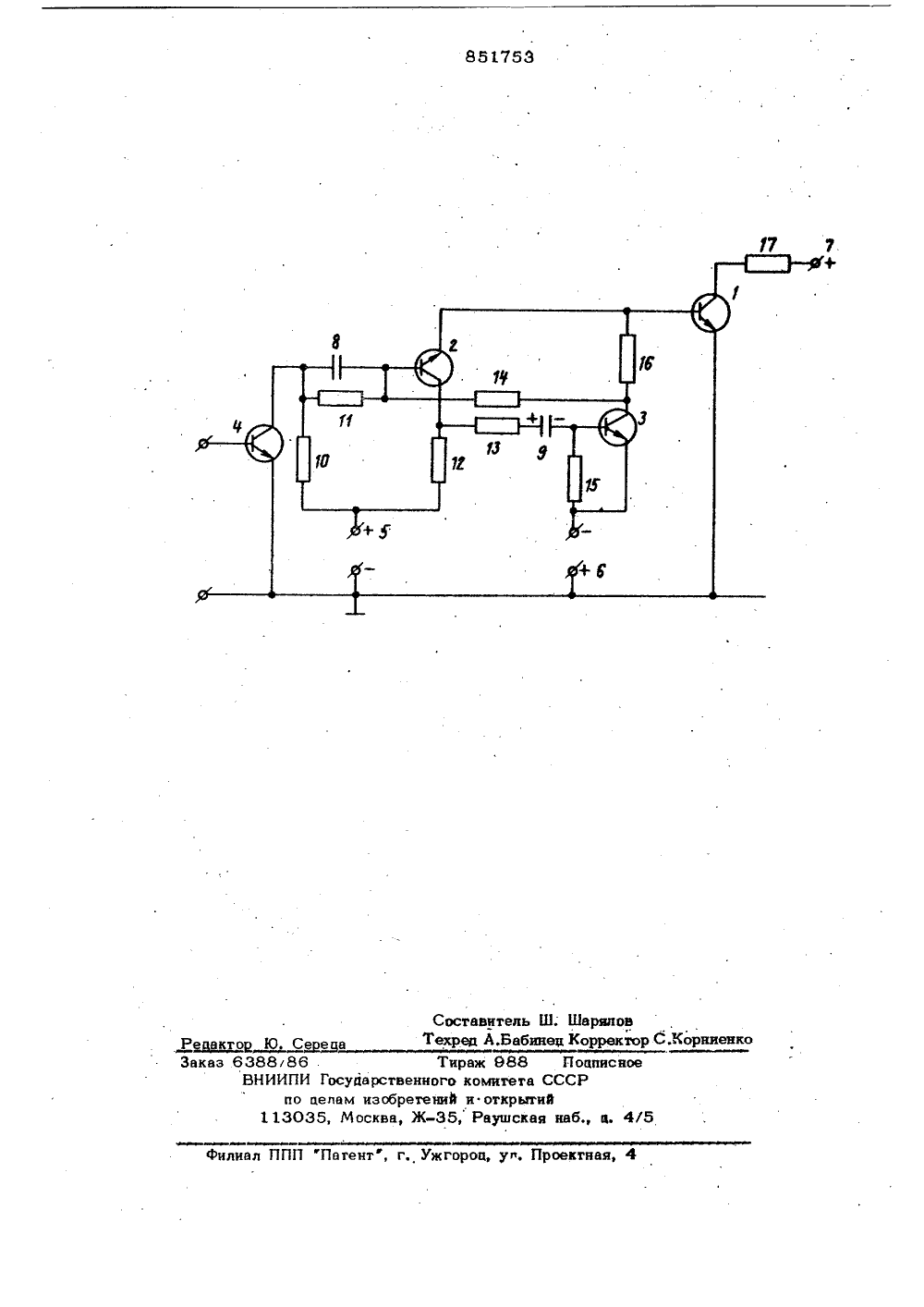

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ц 851753 Союз СоветскихСоциалистическихРеспублик(22) Заявлено 23,10.79(21) 2834072 /18-21с присоединением заявки РйН 03 К 5/02 1 йеудлрстеенных кемнтет СССР йа делам нзевретеннй н еткрытнй(7 ) Заявитель Челябинский политехнический институт им. Ленинского. комсомола(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ Изобретение относится к э"ектроэро-зионной обработке и может быть использовано в преобразовательной технике.Известно устройство, содержащее входной усилитель, запирающие и насыщающиевключи, источники насьпуения и запирания 1"1 5Указанное устройство имеет слецушиенедостатки: отсуствие обшей точки между источником входного сигнала и выхопнкм транзистором при коммутации вы 10хопного транзистора возможны сквозныеточки через транзисторы; из-за использования последовательного управления насьхцаюшим ключом ухупшаются частотныесвойства ключа. Известен транзисторный ключ, содержащий выходной транзистор, запирающийи насьпцаюший ключи, источники наськцения и запирания; вхопной усилитель.Устройство имеет общую точку у источниковнасьпцения и запирания и вхопного и вы-,ходного устройств 2.Указанное устройство имеет недостаточное высокое быстродействие,2Цель изобретения - повышение быстродействия., Поставленная цель постигается тем, что в формирователе импульсов, содержащем четнре транзистора и три источника питания, эмиттер первого из трех транзисторов типа И-р-й соединен с общей шиной, коллектор через нагрузку подключен к положительной шине первого источника питания, база соединена с эмиттером второго транзистора, коллектор и база которого соответственно через резистор соединены с положительной шиной второго источника питания и с коллектором третьего транзистора, база которого через резистор подключена к отрицательной шине третьего, источника питания, четвертый транзистоо имеет проводимость типа И-р-И, база этого транзистора соединена с источником формуруемых импульсов, эмиттер подключен и обшей щи. не, коллекторсоединенчерез резистор с положительной шиной второго источника питания и через параллельную ЙС-цепь5 851 с базой второго транзистора, коллектор которого через последовательнуюС-цепь соединен с базой третьего транзистора, эмиттер третьего транзистора соединен с отрицательной шиной третьего источника питания, а его коллектор через резистор соединен с базой первого транзис тора.На чертеже представлена принципиальная электрическая схема устройства,формирователь импульсов соаержит транзисторы 1-4, источники 5-7 питания, конаенсаторы 8 и 9, резисторы 10-17, Конденсатор 8 и резистор 11 образуют параллельнуо ЙС-цепь, резистор 13 и конденсатор 9 - последовательную ЙСцепь.формирователь работает слеаующнм образом.Примем исходное состояние схемы следующим: транзистор 1 включен и насыщен. При этом на вход устройства подан сигнал нулевого уровня. Тренэистор.4 закрытТранзистор 2 открыт эа счет подачи положительного смешения от источ- ника 5 через резисторы 10 и 11, От источника 5 насыщения протекает, ток по цепи: резистор 12, транзистор 2, эмиттерный переход транзистора 1. Конценсатор 9 заряжен с полярностью, указанной на чертеже, до напряжения источнике 6, так как потенциал коллектора транзистора 2 близок к потенциалу земли. Пусть на вход транзистора 4 поступает положительный сигнал. Тогда транзистор35 4 включается, а транзистор 2 форсированно эакрьвается через конденсатор 8.Так как потенциал транзистора 2 резко возрастает, то появляется импульс тока в цепи: источник 5, резистор 12, резистор 13, конденсатор 9, база-емйттер трап- энстора:5, йсточник 6 питания. Итак, црохоцит форсированное включение транзистора 3. При этом возникает ток запирания во входной цепи транзистора 1 по контуру: источвик 8, база-емиттер траи-зистора 1, резистор 16, транзистор 3, Падение наряжения на резвсторе 16 является. сигналом обратной связи, которая действует на транзистор 2 совместно с запирающим сигналом. Таким образом, повышается быстродействие схемы управления при выключении выходного транзистора 1 и исключается протекание сквозных. токов врез транзисторы 2 н 3. Конценсатор 9 заряжается йосле включения транзистора 3 цо суммы напряжений источников 5 и 6 с той же полярвостью, показанной иа чертеже. 753 6Пусть на вход устройства поступает сигнал нулевого уровня. При этом транзистор 4 закрьвается, а транзистор 2 форсированно открывается, Тогда происходит разряд конденсатора 9 по цепи: выходная цепь транзистора 2 базе-эмизтер транзистора 1, источник 6 и паралельно соединенные база-эмиттер транзистора 3, резистор 15. Этот ток разряда одновременно служит аля форсированного включения транзистора 3. Черезтранзистор 2 протекает насыщающий ток от источников 5.Таким обрадом, ввецение в предлагаемое устройство форсирующих двусторонних обратных связей способствует сокрацению процессов одного типа проводимости, что позволяет осуществить интегральное исполнение схемы.формула нэобре те ни я формирователь импульсов, соцержащийчетыре транзистора и три источника питания,эмиттер первого из трех транзисторов типа И-р-п соецинен с общей шиной,коллектор череЬ нагрузку подключен кположительной шине первого источникапитания, база соединена с эмиттеромтранзистора, коллектор и база которогосоответственно через резистор соединеныс положительной шиной второго источника питания и с коллектором третьеготранзистора, база которого через резистор подключена к отрицательной шине третьего источника питания, о т л и ч а -ю щ и й с я тем, что, с целью повышениябыстродействия устройства, четвертыйтранзистор имеет проводимость.И-р-И,база этого транзистора соединена с источником формируемых импульсов, эмиттерподключен к общей шине, коллектор сое;динен через резистор с положительнойшиной второго источника питания и черезпаралельную ЙС-цепь с базой второготранзисторе, коллектор которого черезпоследовательную ЯС-пень соецинен с базоГ третьего транзистора, эмйттер третьего транзистора соединен с отрицательной шиной третьего источника питания, аеко коллектор через резистор соединюс базой первого транзистора.Источникй информации,принятые во внимание при экспертизе:1. Авторское свиаетельство СССРМ 587628, кл. Н 03 К 17/60, 1978.2, Леоненко Л.И. ПолупроводниковыеФорсирующие схемы. М., Энергия, 1974,с. 80, рис. 56 (прототип).Ре Зак Тираж 088 Паарственного комитета СССизобретений и открытийосква, Ж, Раущская наб ис/5 гороц, ул,тная,р тор Ю. Сере е 638886 ВНИИПИ Госу по ведам 113035, Мнал ППП Патент Составитель Ш. Ш Техред АеБабинен К ряловректор С.Корниенко

СмотретьЗаявка

2834072, 23.10.1979

ЧЕЛЯБИНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТИМ. ЛЕНИНСКОГО КОМСОМОЛА

МИНИХАНОВ ВАЛЕЙ ЯКУБОВИЧ, САПРУНОВА НАДЕЖДА МИХАЙЛОВНА, ГЕЛЬМАН МОРИС ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H03K 5/02

Метки: импульсов, формирователь

Опубликовано: 30.07.1981

Код ссылки

<a href="https://patents.su/3-851753-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Устройство для определения разности двухчастот

Следующий патент: Формирователь импульсов

Случайный патент: Способ защиты печатной платы