Аналоговый интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

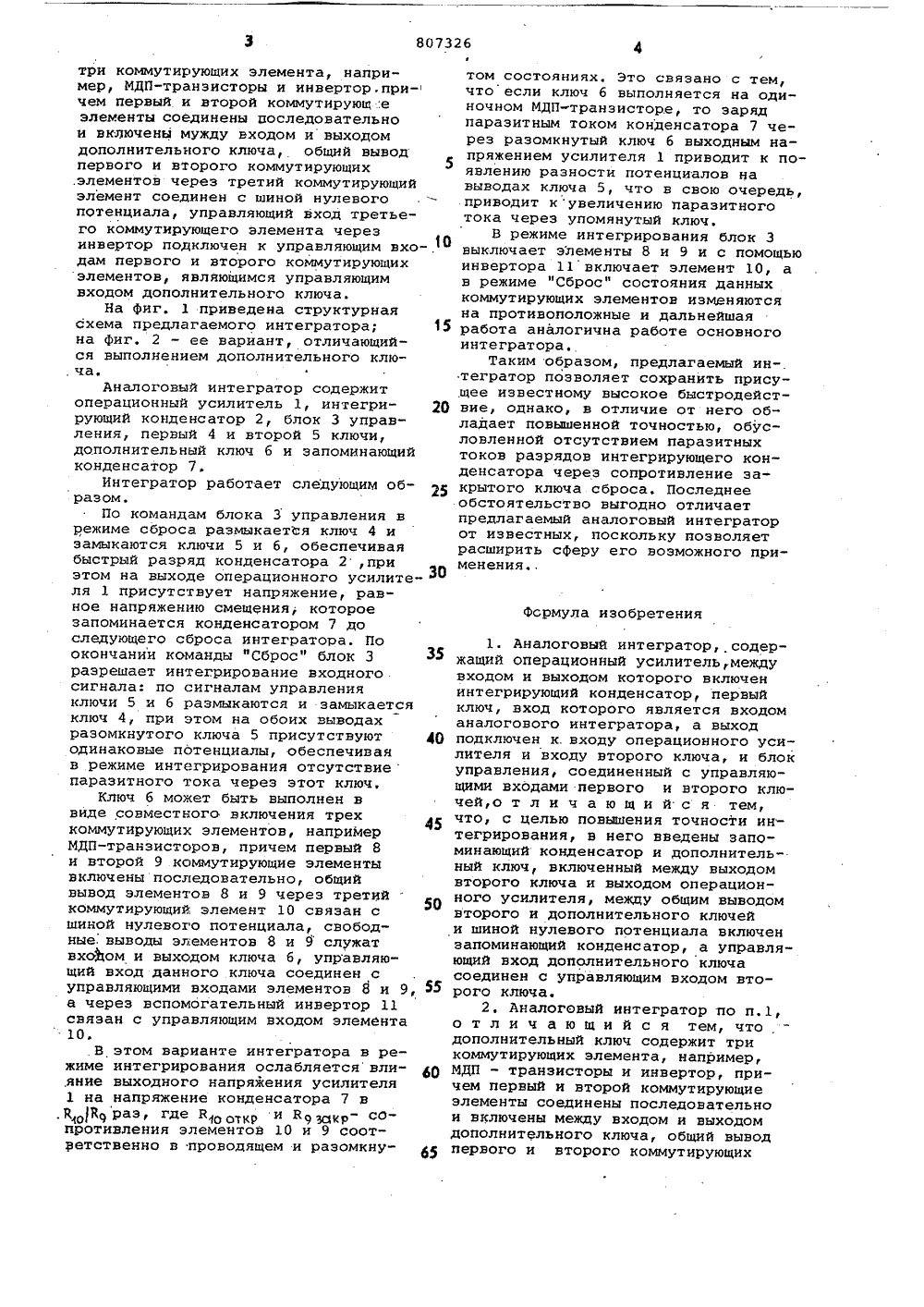

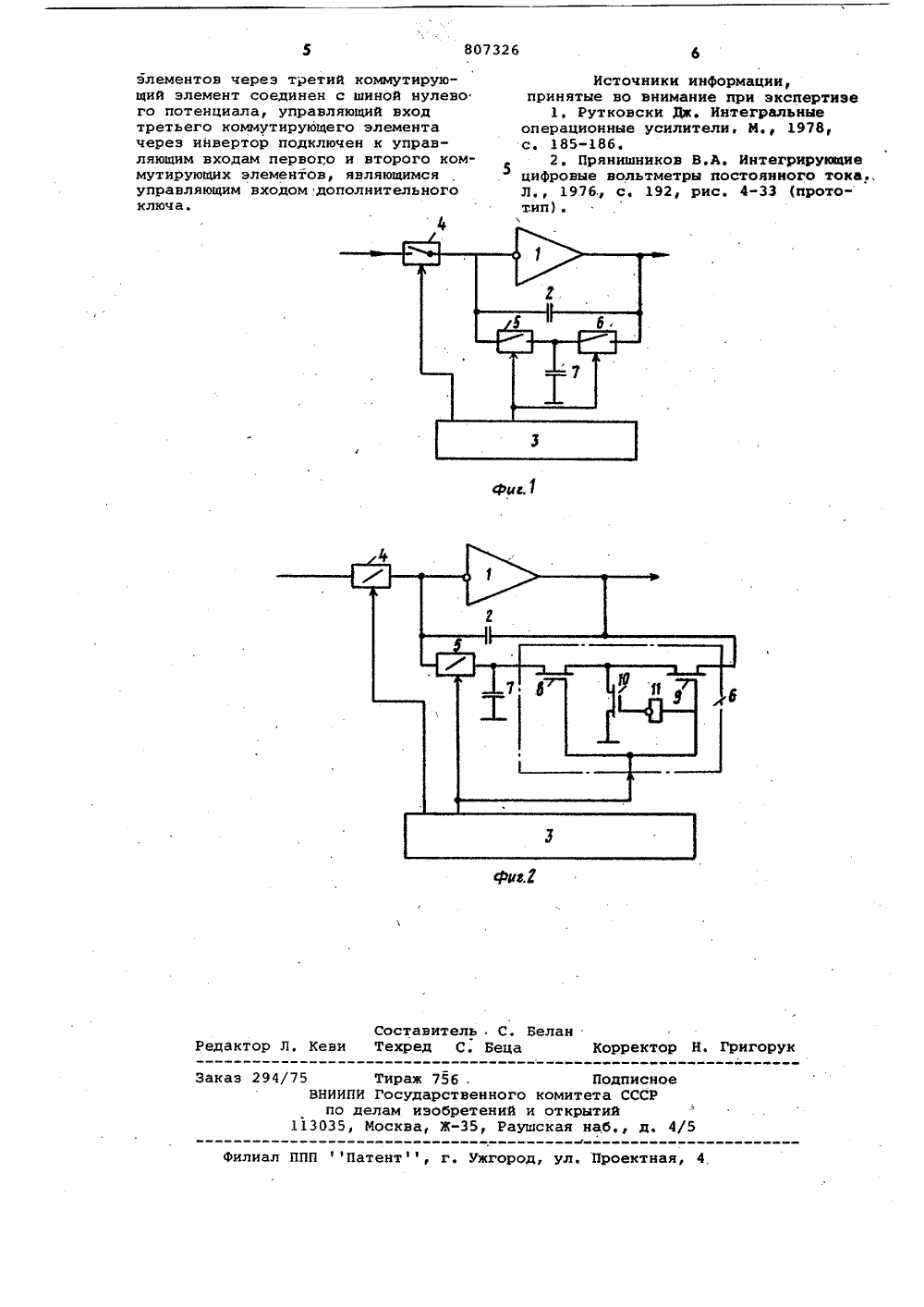

Союз Советских Социалистических Республик(51)м. Кл. с присоединением заявки И 9 а 06 а 7/186 осударствеииый комитет СССР ио делам изобретеиий и открытийОпубликовано 230281. Бюллетень И 9 7 Дата опубликования описания 23.02,81(54) АНАЛОГОВЫЙ ИНТЕГРАТОР 10 15 20 30 Изобретение относится к аналоговой вычислительной технике и можетбыть использовано в аналоговых моделирующих устройствах, а также вэлектронных устройствах различногоназначения,Известны аналоговые интеграторына операционных усилителях, снабжен;ные электромеханическим ключом разряда интегрирующего конденсатора,в которых инвертирующий вход операционного усилителя через параллельно включенные интегрирующийконденсатор и ключ разряда связанс выходом данного усилитеЛя 1,Недостаток подобных интеграторовобусловлен низкимбыстродействиемэлектромеханического ключа разрядаинтегрирующего конденсатора, можетбыть устранен путем замены данногоэлектромеханического ключа электронным элементом,Известен аналоговый интегратортсодержащий операционный усилитель,в цепь обратной связи которого включен конденсатор с электронным ключом разряда 12) .Однако электронные ключи, по сранению с электромеханическими ключами, обладают меньшим сопротивлением в разомкнутом состоянии и поэтомуиспользование в цепи, параллельнойинтегрирующему конденсатору, электронных ключей вызывает погрешностьиз-за паразитного тока, протекающего через разомкнутый ключ,Цель изобретения - повышение точности аналогового интегратора,Поставленная цель достигаетсятем, что в аналоговый интегратор,содержащий операционный усилитель,между входом и выходом которого включен интегрирующий конденсатор,первый ключ, вход которого являетсявходом аналогового интегратора, авыход подключен к входу операционногоусилителя и входу второго ключа, иблок управления, соединенный с управляющими входами первого и второгоключей, введены запоминающий конденсатор и дополнительный ключ, включенный между выходом второго ключаи выходом операционного усилителя,между общим выводом второго и дополнительного ключей и шиной нулевого потенциала включен запоминающийконденсатор, а управляющий вход дополнительного ключа соединен с управляющим входом второго ключа. Приэтом дополнительный ключ:содержит5 О 15 20 25 30 35 40 45 50 55 60 65 три коммутирующих элемента, например, МДП-транзисторы и инвертор,при- чем первый и второй коммутирующ е элементы соединены последовательно и включены мужду входом и выходом дополнительного ключа, общий вывод первого и второго коммутирующих .элементов через третий коммутирующий элемент соединен с шиной нулевого потенциала, управляющий вход третьего коммутирующего элемента через инвертор подключен к управляющим входам первого и второго коммутирующих элементов, являющимся управляющим входом дополнительного ключа.На фиг, 1 приведена структурная схема предлагаемого интегратора; на фиг. 2 - ее вариант, отличающийся выполнением дополнительного клю. ча.Аналоговый интегратор содержит операционный усилитель 1, интегрирующий конденсатор 2, блок 3 управления, первый 4 и второй 5 ключи, дополнительный ключ б и запоминающий конденсатор 7.Интегратор работает следующим образом.По командам блока 3 управления в режиме сброса размыкается ключ 4 и замыкаются ключи 5 и б, обеспечивая быстрый разряд конденсатора 2 ,при этом на выходе операционного усилителя 1 присутствует напряжение, равное напряжению смещения, которое запоминается конденсатором 7 до следующего сброса интегратора. По окончании команды "Сброс" блок 3 разрешает интегрирование входного сигнала: по сигналам управления ключи 5 и б размыкаются и замыкается ключ 4, при этом на обоих выводах разомкнутого ключа 5 присутствуют одинаковые потенциалы, обеспечивая в режиме интегрирования отсутствиепаразитного тока через этот ключ,Ключ б может быть выполнен в виде совместного включения трех коммутирующих элементов, например МДП-транзисторов, причем первый 8 и второй 9 коммутирующие элементы включены последовательно, общий вывод элементов 8 и 9 через третий коммутирующий элемент 10 связан с шиной нулевого потенциала, свободные. выводы элементов 8 и 9 служат входом и выходом ключа б, управляющий вход данного ключа соединен с управляющими входами элементов 8 и 9, а через вспомогательный инвертор 11 связан с управляющим входом элемента 10..В этом варианте интегратора в режиме интегрирования ослабляетсявлияние выходного напряжения усилителя 1 на напряжение конденсатора 7 в "оЯ 9 раэ, где В 1 ооткР и В 93 акР сопротивления элементов 10 и 9 соответственно в проводящем и разомкнутом состояниях. Это связано с тем,чтоесли ключ б выполняется на одиночном МДП-транзисторе, то зарядпаразитным током конденсатора 7 через разомкнутый ключ б выходным напряжением усилителя 1 приводит к появлению разности потенциалов Навыводах ключа 5, что в свою очередь,приводит кувеличению паразитноготока через упомянутый ключ.В режиме интегрирования блок 3выключает элементы 8 и 9 и с помощьюинвертора 11 включает элемент 10, ав режиме "Сброс" состояния данныхкоммутирующих элементов изменяютсяна противоположные и дальнейшаяработа аналогична работе основногоинтегратора.Таким образом, предлагаемый интегратор позволяет сохранить присущее известному высокое быстродействие, однако, в отличие от него обладает повышенной точностью, обусловленной отсутствием паразитныхтоков разрядов интегрирующего конденсатора через сопротивление закрытого ключа сброса, Последнееобстоятельство выгодно отличаетпредлагаемый аналоговый интеграторот известных, поскольку позволяетрасширить сферу его возможного применения.,фсрмула изобретения1. Аналоговый интегратор, содержащий операционный усилитель, между входом и выходом которого включен интегрирующий конденсатор, первый ключ, вход которого является входом аналогового интегратора, а выход подключен к.входу операционного усилителя и входу второго ключа, и блок управления, соединенный с управляющими входами первого и второго ключей,о т л и ч а ю щ и й с я тем, что, с целью повышения точности интегрирования, в него введены запоминающий конденсатор и дополнительный ключ, включенный между выходом второго ключа и выходом операционного усилителя, между общим выводом второго и дополнительного ключей и шиной нулевого потенциала включен запоминающий конденсатор, а управляющий вход дополнительного ключа соединен с управляющим входом второго ключа.2. Аналоговый интегратор по п,1, о т л и ч а ю щ и й с я тем, что,- дополнительный ключ содержит три коммутирующих элемента, например, МДП - транзисторы и инвертор, причем первый и второй коммутирующие элементы соединены последовательно и включены между входом и выходом дополнительного ключа, общий вывод первого и второго коммутирующих807326 ис Составитель С. Беланеви Техред С. Беца Корректо актор Григорук 294/75 ВНИИП по д 113035, Тираж Госуд лам и Москва 56 . Подписи ственного комитета СССР бретений и открытий Ж, Раушская наб., д. ака илнал ППП Патентф, г. Ужгород, ул. Проектная, 4 элементов через третий коммутирующий элемент соединен с шиной нулевого потенциала, управляющий входтретьего коммутирующего элементачерез инвертор подключен к управляющим входам первого и второго коммутирующих элементов, являющимсяуправляющим входом дополнительногоключа. Источники информации,принятые во внимание при экспертизе1. Рутковски Дж, Интегральныеоперационные усилители, М., 1978,с. 185-186.2. Прянишников В.А. Интегрирующиецифровые вольтметры постоянного тока.,Л 1976., с. 192, рис. 4-33 (прототип).

СмотретьЗаявка

2733417, 05.03.1979

ПРЕДПРИЯТИЕ ПЯ Р-4377

ВОЛЫНСКИЙ АЛЕКСАНДР ЕВГЕНЬЕВИЧ, РАЧИН СОЛОМОН АБРАМОВИЧ, СМИРНОВ АНДРЕЙ АЛЕКСЕЕВИЧ, ХАЙТИН АНАТОЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06G 7/186

Метки: аналоговый, интегратор

Опубликовано: 23.02.1981

Код ссылки

<a href="https://patents.su/3-807326-analogovyjj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый интегратор</a>

Предыдущий патент: Устройство для определения знакапервой производной

Следующий патент: Интегратор

Случайный патент: Устройство тепловой изоляции для паропроводов и т. п.