Устройство для цифрового усреднения двоично-кодированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 694867

Автор: Вайнштейн

Текст

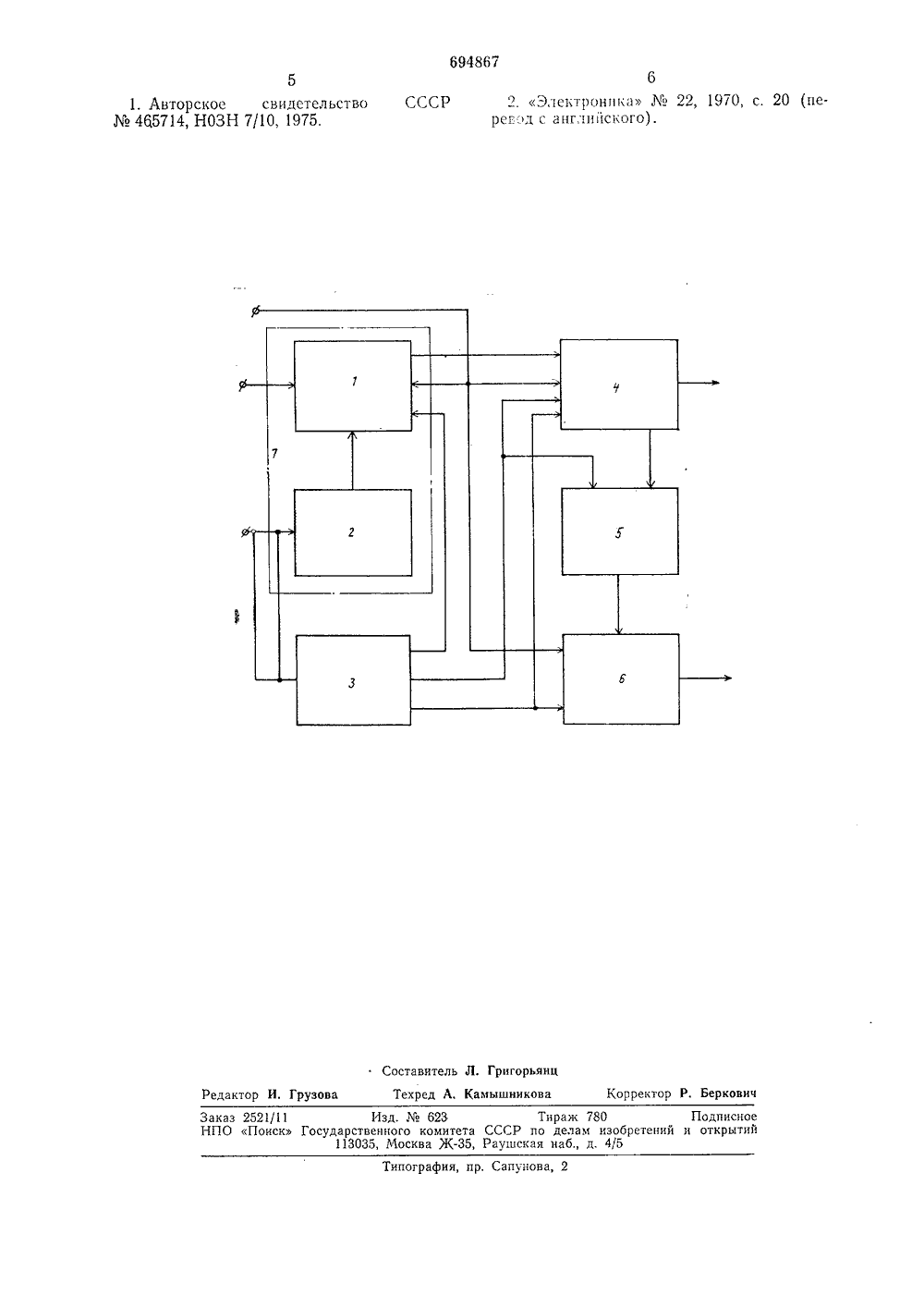

1111694867 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советских Социалистических РеспубликТОРСКОМУ СВИДЕТЕЛЬСТВУ опол 1 штельиое к авт. свид-ву 2394955;18(,1) 55. Кл.-6 06 Г 15)3 1 И ЛО трисоедииечшсм заяв Государственный комитет(43) Опубликовано 30.10,79 Ечоллетеиь ЛЪ 40 (45) Дата опубликования описания 30.10.79 делам изобретений и открьпий(54) УСТРОЙСТВО ДЛЯ ЦИФР СРЕДНЕНИЯ ДВОИЧНО-КОДИР СИГНАЛОВОГОАННЫХ 2 версивного счетчика подключен к выходу элемента стробирования, первый вход которого соединен с выходом переноса старшего разряда сумматора, третш 1 вход которого объед 1 шен с вторым входом элемента строоирования и соединен с вторыа 1 выходом Олока управления. Чстиертыи вход су мма 10 ра Ооъединен с первыми входами блока задержки и реверсивного счетчика и является первым входом устроиства. Трстиш выход блока управления иодк;почси к второму входу блока задержки, третий вход которого служит вторым входом ус 1 ройства. 11 ервый вход блока управления ооъсдинен с четвертым входом О:1 Ока задер)к 1 ы 1 и является тре 1 ы 1 м входом устроиства. 11 ервый выход блока управления подключен к управляющему входу реверсивного счетчика, выход которого является первым выходом устройства, а выход сумматора - вторым выходом ус- тройства Кромеэлсмсп того, блопам 51 ги и с СИ К 1 СРВОХй, трс 1 ий 1 о соо 1 встс входы оло51 СТС 51 1 СТВС 1 ОДКЛ 1 ОЧИ, В 1 ОР )Ого - Э 1 ТРС 1 И 1 чи 1 а явл 22) Заявлено 09.08.76 (2 Изобретение относится к специализированным средствам вычислительной техники и предназначено для обработки цифровых сигналов.Известно устройство для усреднения дво ично-кодиров анных сигналов 11), содержащее сумматор, реверсивный сче 1 чик, регистры памяти и цифровые иеремиожители чисел. 11 ри использовании этого фильтра для усреднения двоично-кодированных сиг налов возникают ошиоки за счет Округления чисел при цифровом умножении, которые накапливаются из-за наличия оорагной связи, Кроме того, большое количссгво перемножителей усложняет схему. 15Наиболес близким техническим решением к изобретению является устройство, содержащее блок задержки, выход которого подключен к первому входу сумматора, второй вход которого соединен с первым выходом блока управления 2).Недостаток устройства заключается в его сложности из-за наличия перемиожителей и многовходового сумматора.Цель изобретения - упрощение устройства.С этой целью в устройство для цифрового усреднения двоично-кодированных сигналов введены реверсивный счетчик и элемент стробирования. При этом счетный вход ре задержки содержит чстчик, выход которого у входу элемента памячетвертый входы кото 1 вснио первый, второй а задержки, вход счстртым входом блока за 694%7деря;и, г вьход э,Оса игг) г - ьходОм блОка задержки.Блок-схема устройства представлен на чертеже.Устройство содержит элемент 1 па,яти, сгстчпк 2, Олок 3 управления, с.ато 1) 1, эл;мент 5 стробпроваппя, реверсвный счетчик 6, Эггемснт 1 памяти и счс г;к 2 образуют блок 7 задержки.Работает устройсво следОспп: образом.Г 1 срсд началом работы вес ячейки элемента 1 ггагятгг, все разряды пгка,ггвс- щего сумматора 4 и реверсивного счетчика 6 по сигналу установки в псходнос. положение, поступающему на псрвый вход усройства, устапавлпваотся в пулевое состояние. Затем на второй вход устройства подастся двоична-кодированный сп.пал, а па третий вход устройспа ( зход счетчика 2 и блока 3 управлепи) - импульсы тактовой частоты. Сип-алы с выхода разрядов счетчика 2 поступают на адресные входы элемента 1 ах,гтн, Ьлогс 3 управления формирует ца выходе сигнал, управляющий работой элемента 1, на втором выходе - стробирукщпй импульс, а на перлом выходе - сш нал, переключающий сумматор 4 и реверспвный счетчик 6 в реяим сложения и;и вычитания,При каждом состоянии счетчика 2 производятся считывание двопчно-кодирсванного сигнала из определенных ячеек элемента 1 памяти и вычитание его из содержимого накапливающего сумматора 4 и реверсивного счетчика 6. Затем осуществляется запись нового значения двоичнокодированного сигнала в те жс ячейки элсмснта памяти - и одновременно сложение его с новым содержимым накаплпвающсго сумматора. Выход переноса старшего разряда накапливающего сумматора - вычптателя через элемент 5 стробироваппя подключен к счетному входу реверсивного счетчика 6, Выходной сигнал спимасгся с первого и второго выходов устройства. Очередной тактовый импульс изменяет состояние счетчика 2, и описанный процесс повторяется с использованием других ячеек элс мента памяти. Таким образом, начиная с момента прихода гг-г выборки двоично-кодированного сигнала, содеркимг накапливающего сумматора 4 и реверсивного счетчика 6 будет сумма последних выборок двоично-кодированного сигнала, которая с приходом каясдой новой выборки сигнала будет уточняться, а не вычисляться заново.Для получения среднего значения необходимо умнояить выходной сигнал на 1/гг. Чтобы избавиться от операции умнон(ения, и выбирается равным целой степени числа 2, а выходам разрядов среднего значс 510 5 20 3 О 35 40 5 50 55 ао 65 ия двопчго-кодироваг;О огг;, г; пр- Сгггппагогх я ГООтВСтстнуЮщпе дВОПЧНЫС ВЕ- са.11 а входног сигнал схемы наложено ограничение - все двои-шыс числа, которым Оп кодируется, должны быть положительными, 11 ри необходимости обработки отрицательных чисел достаточно осуществить простое прс.образование кода на входе и ыходс схс:гы, например на входе преобразовать отрицательные числа вида О Х Х.Х ь где первый разряд знаковый, в числа О Хь Х 2Хг, осгавив положигельные числа наизмснными, а на выходе осуществить обратное преобразование,11 реимущсство изобретсния состоит в том, что оно позволяст,нростить устройство за счет введения реверсивного счетчика, элемента стробированпя и замены многовходового сумматора одновходовым накапливающим сумматором.Формула изобретенияУстройсгво для цифрового усреднения двопчно-кодированных сигналов, содержащее блок задержки, выход которого подключен к первому входу сумматора, второй вход которого соединен с первым выходом блока управлс:ния, отл и ч а ю щесся тем, что, с целью упрощения устройства, в него введены реверсивный счетчик и элемент стробирования, при этом счетный вход реверсивного счетчика подклгочен к выходу элемента стробирования, первый вход которого соединен с выходом переноса старшего разряда сумматора, третий вход которого объединен с вторым входом элемента стробировання и соединен с вторым выходом блока управления, четвертый вход сумматора объединен с первыми входами блока задержки и реверсивного счетчика и является первым входом устройства, третий выход блока управления подключен к второму входу блока задержки, третий вход которого является вторым входом устройства, первый вход блока управления объединен с четвертым входом блока задержки и является третьим входом устройства, первый выход блока управления подключен к управлягощему входу реверсивного счетчика, выход которого является первым выходом устройства, а выход сумматора является вторым выходом устройства.2. Устройство по п, 1, отличающееся тем, что блок задержки содержит элемент памяти и счетчик, выход которого подключен к первому входу элемента памяти, второй, третий и четвертый входы которого являются соответственно первым, вторым и третьим входами блока задержки, вход счетчика является четвертым входом блока задержки, а выход элемента памяти - выходом блока задержки.Источники информации,припятыс во внимание при экспертизеЗаказ 2521/11 Изд.623 Тираж 780 Подписное НПО Поиск Государственного комитета СССР по делам изобретений и открытий 113035, Москва Ж, Раушская наб., д. 4/5

СмотретьЗаявка

2394955, 09.08.1976

ПРЕДПРИЯТИЕ ПЯ А-7672

ВАЙНШТЕЙН БОРИС ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: двоично-кодированных, сигналов, усреднения, цифрового

Опубликовано: 30.10.1979

Код ссылки

<a href="https://patents.su/3-694867-ustrojjstvo-dlya-cifrovogo-usredneniya-dvoichno-kodirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для цифрового усреднения двоично-кодированных сигналов</a>

Предыдущий патент: Цифровое устройство для вычисления синусно-косинусных функций

Следующий патент: Дифференцирующее устройство

Случайный патент: Подбарабанье молотильного аппарата