Аналоговый интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 642721

Автор: Морозов

Текст

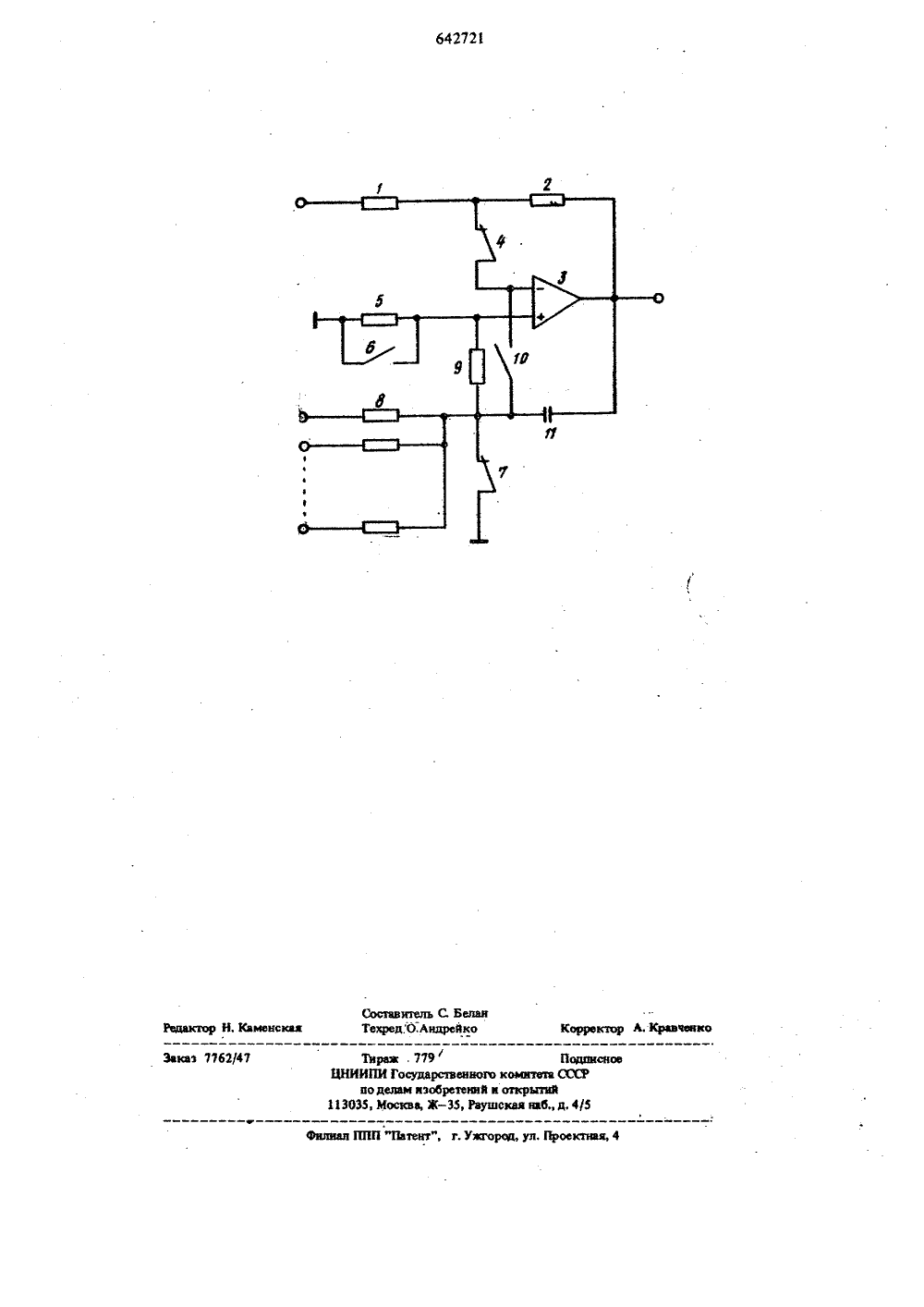

Союз Соватских Соцналнстнчесиих Республик) 2513002/18. 6 718 явки присоединение 3) Приоритет -ааударстаанкый каСССРпв делам кзобрвтан аткрмтий вано 15,01.79, Бюллетень2 бликования описания 15.01.79 3) УЙК 681.335 (088,8) лико Да. П. Мороз ститут проблем упр с дена Ле) Заявнтел АЛОГОВЫЙ ИНТЕГРАТОР о для аналоговых ельных устройств, пения сменой ре. Им вы%щдщ требую тение предназнач льных и нзмер щих логического управ ен с шиной нулевого ные резисторы - со жимов,Аналоговые интеграто управлением режимами но ных ключей известны и испо в аналоговых машинах с паре логичтвом эл ескимтрон ьзуются, нап одизацией ре носности пенн нолшин Недостаток таких интеграторов заключается в невысокой точности интегрирования.Наиболее близок к предложенному интегра. тор, содержащий дифференциальный усилитель, выход которого через два носледовательно соединенных резистора начальных условий подключен к источнику напряжения начальных условий, общий вывод резисторов начальных условий через первый размыкающий ключ соединен с инверсным входом дифференциального усилителя, связанным через последовательно соединенные замыкающий ключ и интегрирующий конденсатор с выходом дифференциального усилителя, общий вывод интегрирующего конденсатора и замыкающего ключа через второй размыкающии ключ соединпотенциала и через масштабвходами интегратора 12) .На сопротивлении замкнутого при вводе начальных условий ключа, соединяющего общий вывод масштабных резисторов и интегрирующего конденсатора обратной связи с шиной нуяевого потенциала (это сопротивление имеет величину порядка десятков или сотен Ом), создается падение напряжения от входных токов интегратора о и тока зарядки конденсатораи, как следствие,возникает. ошибка в начальных условиях, что приводит к снижению точности интегрирования. Целью изобретения является повышение точти интегрирования путем уменьшения огреш.установки начальных условий.Это достигается тем, что в предлагаемый егратор введены дополнительные резисторы и юч, причем нею версный вход дифференального усилителя через параллельно соедиые первый дополнительный резистор и до. нительный замыкающий ключ подключен к е нулевого потенциала н через второй допол20 2 ЭО М 4 О 45 нительный резистор - к общему выводу масштабных резисторов.Структурная схема предлагаемого аналогового интегратора показана на чертеже. Интегратор содержит резисторы начальных условий 1 и 2, одними выводами соединенные соответственно с источником напряжения на. чальных условий и выходом дифференциального усилителя 3, а другими выводами, объединен. ными вместе, - с инверсным входом дифферен. циального усилителя,З через размыкающий ключ 4. Дополнительный резистор 5 включен между неинверсным входом дифференциального уси. лителя 3 и шиной нулевого потенциала, замыкающий ключ 6 включен параллельно резистору 5, размыкающий ключ 7 включен между точкой соединения масштабных резисторов 8, второго дополнительного резистора 9, размыкающего клюю 1 О, подключенного к щшерсному входу дифференциального усилителя 3, интегрирующего конденсатора 11 и шиной нулевого потейциала.,Напряжение ошибки начальных условий представляет собой падение напряжения на ключе 7, Е иеинверсиому входу дифференциального усилителя через делитель, образованный резисторами 9, 5 подводится половина этого напряжения (сопротивления резисторов 9 и 5 равны), Но так как в цепи отрицательной обрат. ной связи, подаваемой на инверсный вход, имеется делитель из резисторов 1 и 2, сопротивления которых равны, то усиление по неинверсному входу равно двум, и напряжение ошибки на выходе дифференциального усилителя по вели. чине и знаку совпадает с напряжением на ключе 7, Поэтому в напряжение начальных условий, равное разности потенциалов на зажимах интегрирующего конденсатора 11 обратной связи, напря. жение ошибки не войдет н погрешность уста. павки начальных условий существенно снизится,В режиме интегрирования состояния всех ключей в устройстве меняются на противоположные и неинверсный вход, соединенный через ключ 6 с шиной нулевого потенциала, не оказы. вает влияния на работу устройства. Резистор 9, подключенный в этом режиме межпу сумми. рующей точкой интегратора н шиной нулевого потенциала, также практически не влияет на ра. боту схемы,В предложенном устройстве за счет введения небольшого числа дополнительных элементов удается увеличить точность интегрирования путем уменьшешя погрецшости ввода начальных ус. ловий, обусловленной конечным сопротивлением электронного ключа, через который заряжается конденсатор обратной связи,Формула изобретения Аналоговый интегратор, содержащий диф. ференциальный усилитель, выход которого через два последовательно соединенных резистора начальных условий подключен к источнику напряжения начальных условий, общий вывод резисторов начальных условий через первый размыкающий ключ соединен с инверсным входом ( дифференциального усилителя, связанным через последовательно соединенные замыкающий ключ и интегрирующий конденсатор с выходом дифференциального усилителя, общий вывод интегрирующего конденсатора и замыкающего ключа через второй, размыкающий ключ соединен с шиной нулевого потенциааа и через масштабные резисторы - совходами интегратора, о тл ич а ю щ ий с я тем, что,с целью повышения точ. ности интегрирования путем уменьшения погреш. ности установки начальных условий, в него введены дополнителыгые резисторы и ключ, причем неинверсиый. вход дифференциального усилителя через параллельно соединенные первый дополнительный резистор и дополнительный замыкающий ключ подключен к шине нулевого потенциала и через второй дополнительный резистор - к общему выводу масштабных резисторов.Источники информации, принятые во внимание при экспертизе1. Сборник статей Гибридная вычислительная система ГВС, Аппаратура и принципы ее построения", Институт проблем управ. пения. М 1974, с, 70,2, Корн Г., Кори Т. "Электронные аналого.вые и аналого. цифровые вычислительные машины" М., "Мир", 1968, с. 56.642721 стор Н, Каменская каз 7762/47 ПодписноеССО,набд, 4/5 ул, Проектная, 4 Составитель С БеланТехред,О,Андрейко Зарем . 779 ЦНИИПИ Государственного коинтета до денни изобретений н откр 113035, Москва, Ж, Рауаскал

СмотретьЗаявка

2513002, 26.07.1977

ОРДЕНА ЛЕНИНА ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ АН СССР

МОРОЗОВ ВИТАЛИЙ ПАНТЕЛЕЙМОНОВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: аналоговый, интегратор

Опубликовано: 15.01.1979

Код ссылки

<a href="https://patents.su/3-642721-analogovyjj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый интегратор</a>

Предыдущий патент: Пневматическое устройство для вычисления модуля

Следующий патент: Дифференцирующее устройство

Случайный патент: Центральное опорное приспособление для железнодорожных сочлененных поворотных кругов