Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

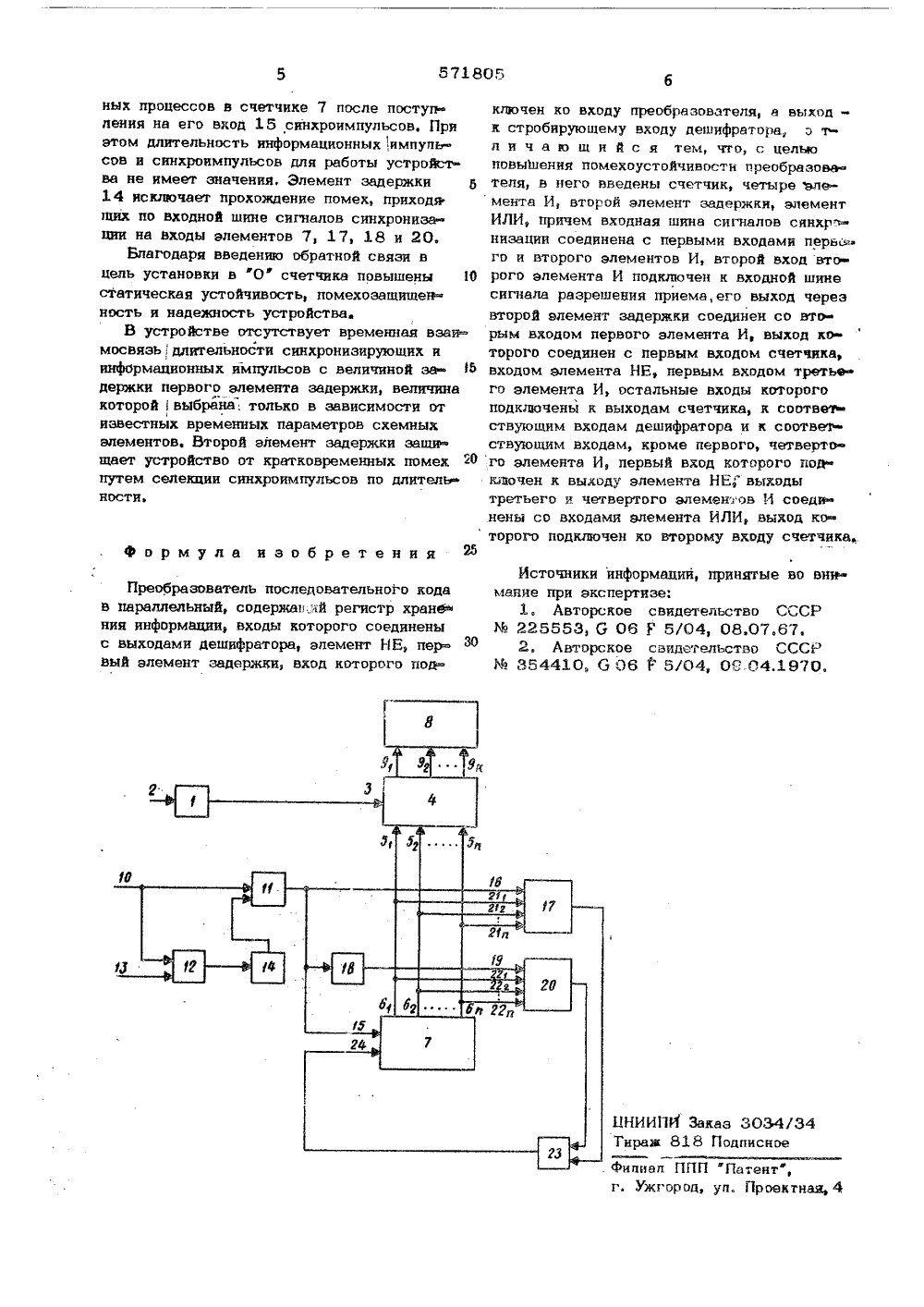

Союз Советскиз Социалистицескин Республик(51) М. Кл,с 6 065/О присоединением заявкиГесуднрственныЯ нсмнтеСеавта Мнннстрсв СССРнн двлнм нэсбретвннЯн стнрытнЯ. И. Шарап Бажлев,. Н. талев ПРЕОБРАЗОВАТЕЛ КОДА Вся повышение Изобретение отйбЬится к области вычис лительной техники и может быть использовано для преобразования последовательного двоичного кода в параллельнЫй,Известен преобразователь последователь ного кода в параллельный, содержащий двух тактный регистр сдвига, блок формирования конца кодовой комбинации и ключи 1).Недостатком устройства является возмо;,и ность возникновения помехи в выходных цэ пях иэ-за переходных процессов в устройстве.Наиболее близким техническим решением к изобретению является преобразователь последовательного кода в параллельный, со держащий регистр хранения информации, вхо 16 ды которого соединены с выходами дешиф ратора, элемент НЕ, первйй элемент задерж.ки, вход которого подключен ко входу пре образователя, а выход " к стробируюшемувходу дешифратора 12 Ц20В этом устройстве для устранения помехи по соседнему разрэщу исттользуются прямой и инверсный сигналы последовательного кода и задерживается информационный импульс по отношению к синхроимпульсу на величину, кб ПОСЛЕДОВАТЕЛЬНОГОАРАЛЛЕЛЬНИй не более половины длйтельности синхроиннф пульса, Однако с уменьшением длительности информационного импульса временной разброс схемы задержки приближается к длительноо ти самого импульса. В результате увеличи вается вероятность перекрытия синхроимпуль сом информационного сигнала, а, следова тельно, возможно появление помехи по со-седнему.разряду.Целью изобретения являетпомехоустойчивости устройства.Эта цель достигается тем, что в предложенный преобразователь последовательного кода в параллельный, содержащий регистр хранения информации, входы которого соединены с выходами дешифратора, элемент НЕ, первый элемент задержки, вход кото рого подключен ко входу преобразователя, а выход к стробирующему входу дешифретора, введены счетчик, четыре элемента И, второй элемент задержки и элемент ИЛИ. Вход ная шина сигналов синхронизации соединена с первММи входами первого и второго эде ментов И. Второй вход второго элемента И подключен к входной шине сигнала разрэщения приема, а выход через второй элемент задержки- ко второму входу первого алемента И, выход которого соединен с первым входом счетчика, входом алемента НЕ и первым входом третьего элемента И. Осталь ные входы третьего элемента И подключены к выходам счетчика, к соответствующим входам дешифратора и к соответствующим входам, кроме первого, четвертого элемента И, первый вход которого подключен к выходу 10 элемента НЕ. Выходы третьего и четвертого элементов И соединены со входами элемента ИЛИвыход которого подключен ко второму входу счетчика.На чертеже изображена блок-схема пред ложенного преобразователя.Преобразователь содержит алемент задержкй 1, вход которого подключен к инфор мационной шине 2, а выход - к стробирующему входу 3 дешифратора 4, другие входы у 5 - 5 п которого соединены с выходами 6 - 6 л счетчика 7 (где й - число разрядов счетчика), регистр 8 хранения информации, входы 9 - 9 к (где х -число разрядов двоичного кода) которого соединены с выхо- Я дами дешифратора 4, Входная шина 10 сигналов синхронизации соединена с первыми входами первого 11 и второго 12 элементов И. Второй вход элемента И 12 соединен с входной шиной 13 сигнала разрешения прие 30 ма, а выход через второй элемент задери ки 14 - со вторым входом элемента И 11, выход которого соещнен с первым счетным входом 15 счетчика 7, со входом 16 третьего элемента И 17 и через элемент НЕ 18 М со входом 19 четвертого элемента И 20.Другие входы 21 - 21 п и 22 - 22 але ментов И 17 и 20 подключены к выходам счетчика 7, Выходы элементовИ 17 и 20 связаны со входами алемента ИЛИ 23, выхоФО которого подсоединен ко входу 24 установки в фОф счетчика 7.Устройство работает следующим образом,В исходном состоянии, когда сигналы на шинах 2 и 10 отсутствуют, счетчик 7 поддерживается.в нулевом состоянии сигналом, поступающим через элемент ИЛИ 23 на выход 24 установки в Оф счетчика 7 с алемента И 17, дешифрующего нулевые щ состояния разрядов счетчика, При подаче по шине 13 сигнала разрешения приема первый синхроимпульс, пришедший по шине 10, открывает элемент И 11 только после того, как атот же синхроимпульс поступит на вто- Ы рой вход элемента И 11 через элемент И 12 и элемент задержки 14. Сигнал с выхода элемента И 11 поступает на вход 16 элемента .,И 17 и закрывает его, В результа те снимается сигнал со входа 24 установки Ю в "0" счетчика 7, поданный на него черезалемент ИЛИ 23. После снятия этого сиъ.нала импульс, пришедший на вход 15 счетчика 7 устанавливает в нем код единицы.Элемент И 17 остается в закрытом состоянии по окончании синхроимпульса благодарясигналу, поступающему с выхода 6 счетчика на вход 21, Последующие синхроимпульсы, приходящие на вход 15 счетчика 7,приводят к появлению единичных сигналов навыходах 6 - 6 п счетчика. Сигналы с выходов счетчика поступают одновременно на входы 5 5 п дешифратора 4 и на входы 2121 элемента И 17.Кодовые импульсы, которые приходят пошине 2 одновременно с синхроимпульсами,поступают через элемент задержки 1 настробирующий вход 3 дешифратора 4. В результате каждому единичному кодовому импульсу соответствует сигнал на том выходедешифратора 4, номер которого соответствуетномеру разряда атого кодового импульса.Импульсы с выходов 9 - 9 с дешифратора4 устанавливают в соответствующих разрядах регистра 8 хранения информации еднничный код,Те разряды регистра, на входы которыхимпульсы не прошли, остаются в нулевомсостоянии,После прохождения всей серии кодовыхимпульсов в регистре 8 запоминается пооледовательный код переданной кодограммы,С приходом М -го сиМроимпульса, .соответствующего последнему разряду принимаемогодвоичного кода, счетчик 7 заполняется. Навходах 22 - 22 д элемента И 20 присутствуют сигналы, а после окончания М -госицхроимпульса появляетсясигнал на входе 19. При этом открывается элемент И 20и на его выходе появляется сигнал, которыйчерез алемент ИЛИ 23 по входу 24 устанавливает счетчик 7 в нулевое состояние.Элемент И 20 закрывается, а элемент И 17открывается, и сигнал на его выходе черезэлемент ИЛИ 23 поддерживает счетчик 7в пулевом положении. Устройство возвращается в исходное состояние.Благодаря статичэской взаимосвязи нулевых состояний:счетчика 7 с. его входомустановки в "0" все устройствс обладаетповышенной устойчивостью к импульснымпомехам, которые могут появиться на входесчетчика.Элемент задержки 1 обеспечивает устранение помехи на входах 9 дешифратора 4от переходных процессов в счетчике и дешисраторе, Величина задержки должна обеспечить приход информационных импульсов навход 3 дешифратора 4 по окончании переход571805 ных процессов в счетчике 7 после поступления на его вход 15 синхроимпульсов. При этом длительность информационных ямпупьсов и синхроимпульсов для работы устройся ва не имеет значении, Элемент задержки к 14 исключает прохождение помех, приходя щих по входной шине сигналов синхронизации на входы элементов 7, 17, 18 и 20.Благодаря введению обратной связи в цель установки в "О счетчика повышены 1 О статическая устойчивость, помехозащищен ность и надежность устройства.В устройстве отсутствует временная взаимосвязь длительности синхронизирующих и информационных импульсов с величиной за В держки первого элемента задержки, величина которойвыбрана, только в зависимости от известных временных параметров схемных элементов. Второй элемент задержки защи. щает устройство от кратковременных помехпутем селекции синхроимпульсов по длитель ности,Формула изобретения Преобразователь последовательного кодав параллельный, содержал.,ий регистр хранбщния информации, входы которого соединеныс выходами дешифратора, элемент НЕ, пер ЗОвый элемент задержки, вход которого под ключен ко входу преобразователя, а выходк стробирующему входу дешифратора о ил и ч а ю щ и й с я тем, что, с цельюповыШения помехоустойчивости преобразоветеля, в него введены счетчик, четыре ълемента И, второй элемент задержки, элементИЛИ, причем входная шина сигналов синхронизации соединена с первыми входами первьго и второго элементов И, второй вход второго элемента И подключен к входной шинесигнала разрешения приема,его выход черезвторой элемент задержки соединен со вторым входом первого элемента И, выход которого соединен с первым входом счетчика,входом элемента НЕ, первым входом третьего элемента И, остальные входы которогоподключены к выходам счетчика, к соотнесствующим входам дешифратора и к соответствующим входам, кроме первого, четвертого элемента И, первый вход которого подключен к выходу элемента НЕ; выходытретьего и четвертого элементов И соединены со входами элемента ИЛИ, выход которого подключен ко второму входу счетчика Источники информации, принятые во внимание при экспертизе:1, Авторское свидетельство СССРИц 225553, б 065/04, 08,07,67,2. Авторское свидетельство СССРЯ Я 5 441 О ( )6 г 5/04 Ос 04 1 970,ЦНИИПЙ Заказ ЗОЗ 4/3Тираж 818 Подписное Фипнап ППП Патент, Ужгород, уп. Проектная,4

СмотретьЗаявка

2147556, 20.06.1975

ПРЕДПРИЯТИЕ ПЯ А-1001

ШАРАПОВА ЗОЯ ИВАНОВНА, БАЗАЛЕВ ЮРИЙ АЛЕКСЕЕВИЧ, ХРУСТАЛЕВ НИКОЛАЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 5/04

Метки: кода, параллельный, последовательного

Опубликовано: 05.09.1977

Код ссылки

<a href="https://patents.su/3-571805-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Устройство для формирования кода сообщения

Следующий патент: Многоуровневое устройство для сравнения

Случайный патент: Способ определения момента касания инструмента с деталью