Запоминающее устройствоiшb=; lrиj•: alh: шi биь.: г-ю-: ;: ; л

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

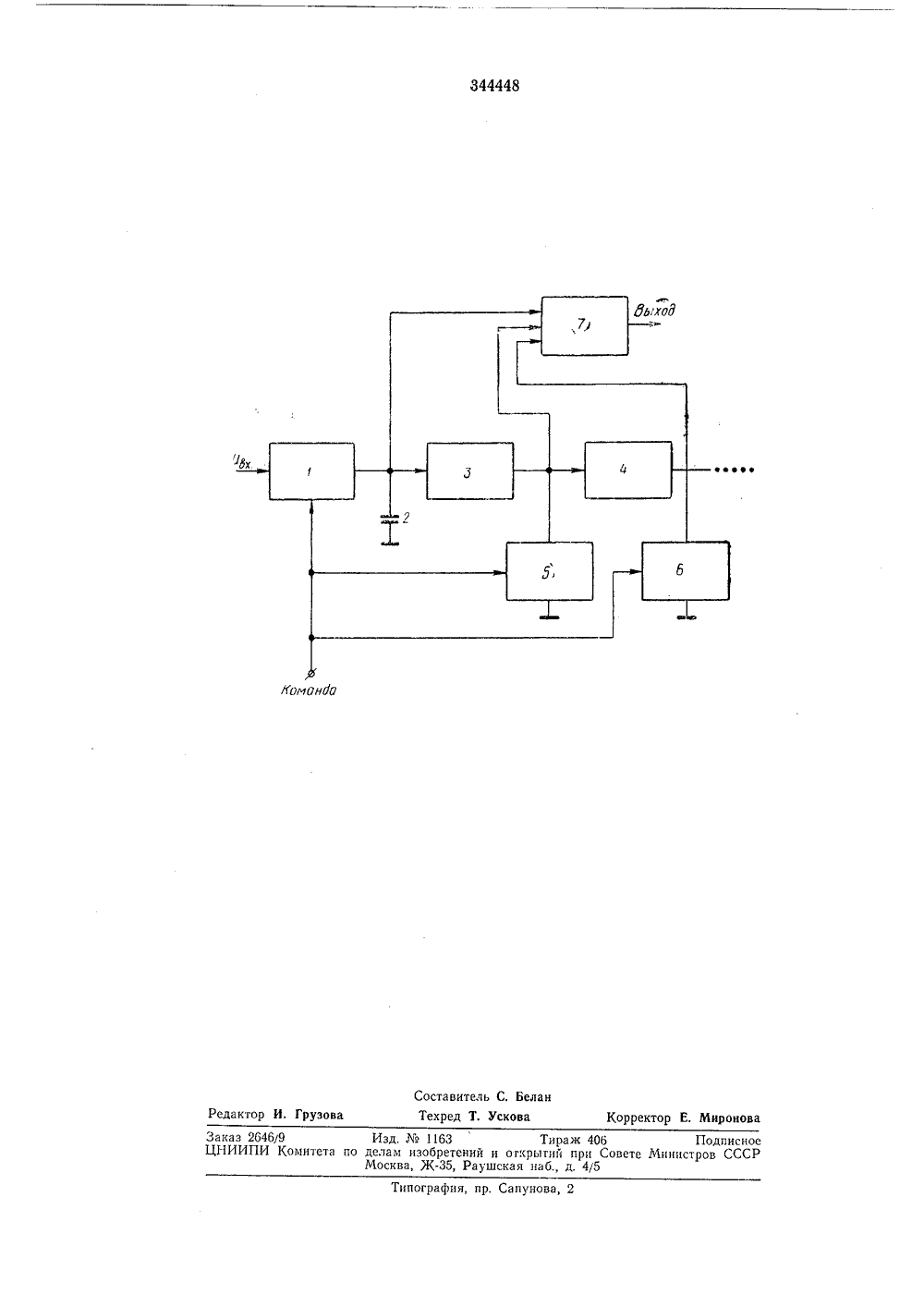

Соаз Советских Социалистических РеспубликЗависимое от авт. свидетельства0 ( 1612752/1 6 д 7/02 1 с 27/О Заявлено аявкис присоединением Комитет по делам зобретений и открытий при Совете Министров СССР. Лес Заявите ПОМИНА 10 ЩЕЕ УСТРОЙСТВО омпен ремен м кон н- ев Изобретение относится к аналоговым запоминающим устройствам, предназначено для запоминания и хранения аналоговых напряжений и может быть использовано в аналоговых и цифро-аналоговых вычислительных машинах.Обработка аналоговых сигналов в вычислительных аналоговых и цифро-аналоговых машинах требует запоминания дискретных значений сигналов при квантовании по времени, при построении линии задержки и т. д, Одной из разновидностей запоминающего устройства является схема, содержащая ключ в цепи запоминаемого сигнала, управляемый командным импульсом, и конденсатор, служащий для хранения информации.Необходи мость считывания запомненной информации приводит к шунтированию конденсатора, что и ограничивает время памяти. Даже при достаточно высоком входном сопротивлении считывающего устройства, выполненного, например, с применением полевых триодов, имеет место утечка, обусловленная конечными значениями сопротивления изоляции конденсатора и сопротивления закрытого ключа.Цель изобретения - увеличение времени хранения информации.Это достигается применением цепи апериодических звеньев, ключей, параллельных их выходам, и сумматора, позволяющих к спровать в ограниченном интервале в и памяти ошибку, обусловленную разрядо денсатора.На чертеже показана схема предлагаемого запоминающего устройства,Запоминающее устройство состоит из ключа 1 в цепи сигнала, конденсатора 2, соедине ных последовательно апериодических звень 3 и 4, ключей 5 и 6, параллельных их выходам, и сумматора 7.Цепи управления всех ключей соединены между собой и с цепью командного импульса, Конденсатор и втяходы всех апериодических звеньев соединены с входами сумматора, а вход первого апериодического звена - с конденсатором.Запоминающее устройство работает следующим образом,При подаче командного импульса все ключи схемы замыкаются. Конденсатор 2 заряжается входным сигналом, а все апериодические звенья 3, 4 и т, д. обнуляются, так как их выходы шунтируются открытыми ключами 5, 6 и т, д. На выходе сумматора 7 появляется сигнал, равный входному. С исчезновением командного импульса все ключи размыкаются. Конденсатор 2 переходит в режим памяти и начинает разряжаться. Постоянная времени разряда конденсатора 2 определяется как3Ур -- СЯ, где Р - сопротивление параллельной цепи из входного сопротивления сумматора (здесь может быть применена развязка), сопротивления утечки конденсатора, сопротивления закрытого ключа и входного сопротивления апериодического звена 3, Одновременно с разрядом конденсатора 2 нарастают напряжения на выходах апериодических звеньев. На выходе сумматора напряжение оказывается равным У. =У,2+К 303+КУ 4+, где У У 4- напряжение на выходах апериодических звеньев 3, 4; К 3, К 4 - коэффициенты.При этом напряжение на конденсаторе 2трУд =У,егде У - запомненный входной сигнал, а навыходах апериодических звеньев- е - сУг =СУг 2 1 - е=Уге Р 1 - е тУ,=Ьс 2 1 - е1 - е=Уер 1 - е 1 - егде Т Т 4 и т, д. постоянные времени апериодических звеньев 8, 4.Таким образом, напряжение на выходе сумматораУе = Уе ее 1 1 + К, 11 - е1 + К,К, ХХ (1 - ее (1 - еилиК:И + Л 1+ Лг+где Л 1, Л 2 и т. д, - ошибки памяти, пропорциональные соответственно 1, Р и т. д. 344448параметры 1(ъ К 4 и т. д т 3, ти т. д, могутбыть выбраны такими, чтобы уменьшить суммарную ошибку памяти или, другими словами, увеличить время памяти, определяемое из 5 менением запомненного напряжения в допустимых пределах, Например, при наличии двух апериодических звеньев 3 и 4 и выбора Т 3 - Т 4 - Тр и КЗ - К 4 - 1Л =Л =0 и ошибки памяти Л Л1 2 3+ 4+При 1,=0,1 Тр, где 1 п - время памяти, суммарная ошибка равна 0,0009 У, тогда как в случае отсутствия апериодических звеньев суммарная ошибка15- СпУ 1 - е Р =- У(1 - е) =0,0952 У,будет достигнута в случае отсутствия апери одических звеньев лишь при 1,=0,001 Тр, т. е.два апериодических звена увеличивают время памяти при заданной ошибке 0,10/О в сто раз,Предмет изобретения25Запоминающее устройство, содержащееключ, управляющий вход которого соединен с источником управляющих сигналов, а выход - с запоминающим конденсатором, отличающе еся тем, что, с целью увеличения времени хранения информации, оно содержит и последовательно сосдиненных апериодических звеньев, дополнительные ключи и сумматор, причем вход первого апериодического звена подклю чен к запоминающему конденсатору и к одному из входов сумматора, другие входы которого подключены к выходам апериодических звеньев, соединенных с сигнальными входами дополнительных ключей, управляющие входы 40 которых подключены к источнику управляющих сигналов,344448мОСоставитель С, Белан Редактор И, Грузова Техред Т. Ускова Корректор Е. МироновЗаказ 2646/9 Изд.П 63 Тираж 406 Подписное ЦНИИПИ Комитета по делам изобретений и огкрытий при Совете Министров СССР Москва, Ж, Раушская наб., д. 4(5Типография, пр. Сапунова,

СмотретьЗаявка

1612752

Т. Г. Голикова, В. И. Кузьмичев, Б. И. Ланцман, В. Г. Лесков, А. Н. Рудаков

МПК / Метки

МПК: G11C 27/00

Метки: lrиj•, б.и, г-ю, запоминающее, устройствоiшb=

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/3-344448-zapominayushhee-ustrojjstvoishb-lrij-alh-shi-bi-g-yu-l.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройствоiшb=; lrиj•: alh: шi биь.: г-ю-: ;: ; л</a>

Предыдущий патент: Пневматический делитель

Следующий патент: Секционированная наборная панель 1.

Случайный патент: Способ соединения стекла с металлом