Всесоюзная 1 г5» г”5чи: . frs: jj-pi lil; «, i. hlj-; ta; • f1, -.; 4

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 374615

Автор: Черн

Текст

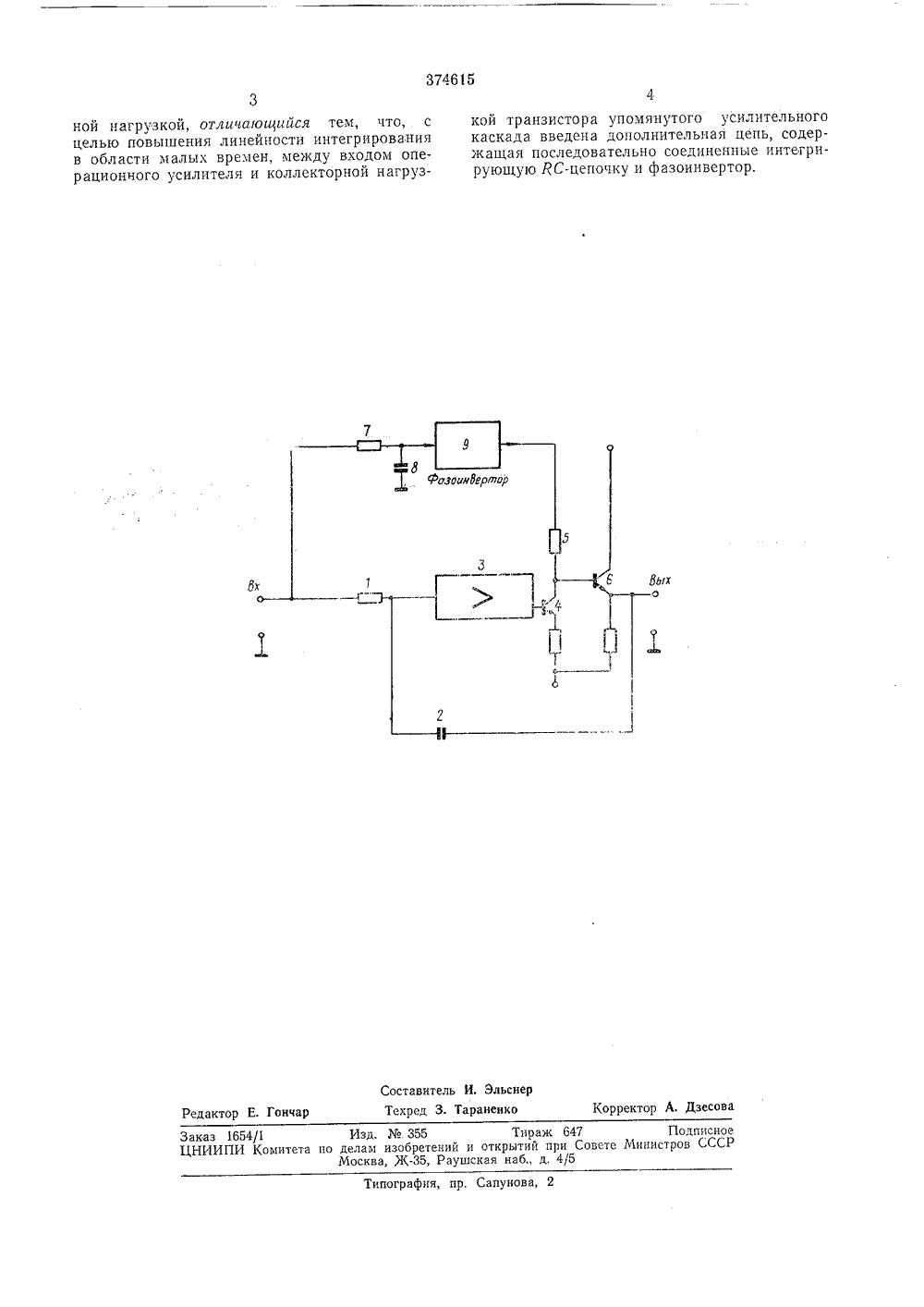

ОПИСАНИЕ ЗУ 46 БИЗОБРЕТЕНИЯК АВТОРСКОМУ СВМДЕТЕЛЬСТВУ Со 1 оз Советекию Социалистическиз республикЗависимое от авт. свидетельства МЗаявлено ЗО,Х 1,1970 ( 1493937/26с присоединением заявкиПриоритет Кл. б 06 д 7/1 комите по делам забретеиий и открытий при Совете Министров СССР"; ",1". г. и 1т"ф П. Черня аявитель НТЕГРАТОР Входной сигнал поступает на интегрирующий решающий усилитель, содержащий решающие элементы 1 и 2, усилитель 3 с выходным каскадом по схеме с общим эмиттером, по строенным на триоде с нагрузочным резистором 5 и умощняющим повторителем 6, и на интегрирующую цепочку, состоящую из элементов 7 и 8, выход которой соединен со входом фазоинвертора 9, а выход фазоинверто ра 9 соединен с нагрузочным резистором Б,Благодаря введению второго канала, удалось обеспечить сохранение линейности вплоть до весьма малых времен, ограниченных в данном случае фактически только широкополос ностью фазоинвертора, которую можно легкосделать большой.Кроме того, благодаря введению второго канала удалось серьезно понизить требования к коэффициенту усиления усилителя и в обла сти средних частот диапазона, так как в области средних времен, лежащих в зоне 0,1 - 0,5 т, второй канал также серьезно корректирует линейность интегратора. едмет изобретения Изобретение относится к области автоматики и предназначено для использования при интегрировании быстропротекающих процессов, в прецизионных преобразователях напряжение - интервал времени и в других устройствах.Известны схемы двухканальных интеграторов, содержащие операционные интегрирующие усилители в основном канале и цепь обратной связи. Однако этим схемам свойственна значительная нелинейность при малом времени интегрирования, обусловленная инерционностью усилителя.Для повышения линейности интегрирования в Области малых времен в интегратор введен второй канал, состоящий из интегрирующей цепочки, имеющей постоянную времени, равную постоянной времени решающей цепи операционного усилителя. Вход цепи соединен со входом интегрирующего решающего усилителя, а выход цепочки соединен со входом фазоинтерсного каскада с низким выходным сопротивлением, нагрузкой которого является выходной каскад решающего усилителя, собранный по схеме с общим эмиттером и умощ ненный на выходе повторителем, а выходной сигнал снимается с выхода интегрирующего решающего усилителя.На чертеже приведена структурная схема устройства, 3 Интегратор, выполненныи на операционном силителе, к выходу которого подключен транзисторный усилительный каскад с разделен374615 рх Составитель И. ЭльснеТехред 3. Тараненко Корректор А. Дзесова Гонца дакт ография, пр. Сапунова, 2 ной нагрузкой, отличающийся тем, что, с целью повышения линейности интегрирования в области малых времен, между входом операционного усилителя и коллекторной нагрузЗаказ 1654/1 Изд. , 355 ЦНИИПИ Комитета по делам изобретМосква, Ж,кой транзистора упомянутого усилительного каскада введена дополнительная цепь, содержагцая последовательно соединенные интегрирую 1 цую ЙС-цепочку и фазоинвертор,Тираж 647 Подписноей и открытий при Совете Министров СССР ушская наб., д. 4/5

СмотретьЗаявка

1493937

С. П. Черн

МПК / Метки

МПК: G06G 7/186

Метки: hlj, jj-pi, всесоюзная, г"5чи, •-•"г5

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/2-374615-vsesoyuznaya-1-g5-g5chi-frs-jj-pi-lil-i-hlj-ta-f1-4.html" target="_blank" rel="follow" title="База патентов СССР">Всесоюзная 1 г5» г”5чи: . frs: jj-pi lil; «, i. hlj-; ta; • f1, -.; 4</a>

Следующий патент: Устройство для получения импульсных сигналов

Случайный патент: Сместитель непрерывного действия