Устройство фазирования для цифровых систем с последовательно-параллельной трансформацией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 295204

Авторы: Воронцов, Полиевский

Текст

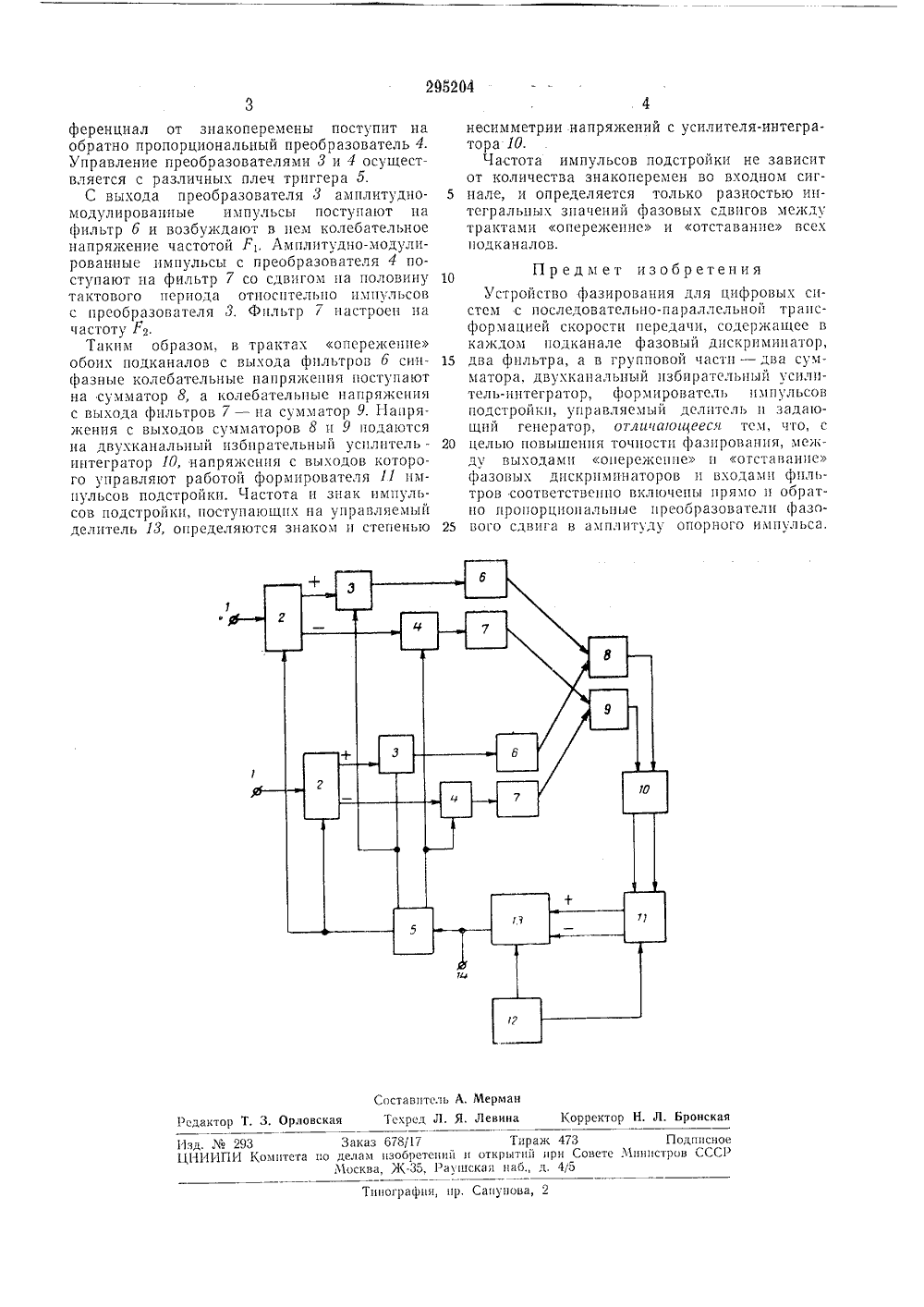

Союз Советских Социалистических Республиквисимое от авт. свидетельства ЛЪ Заявлено 23.Х 11.1968 ( 1 ПК Н 041 7 О1293261/26-9)ки Леъе"т:Фут Г с присоединением заПриоритет Комитет по делам забретений и открытий при Совете Министров СССРК 621.394.662,2 (088,8) Опубликовано 04,1.1971. Бюллетень Лв 7 ата опубликования писания 19.11.19 Авторы зобретени Г. А. Полиевский и В. А. Воронцов Заявител УСТРОЙСТВО ФАЗИРОВАНИЯ ДЛЯ ЦИФРОВЫХ СИСТЕМС ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛ ЕЛ Ь НО Й ТРАН СФОРМАЦИ СКОРОСТИ ПЕРЕДАЧИ ройство фазирования с транс- рости манипуляции, в котором б опорном напряжении выдео (любого) параллельного под 5 известного устройства являетть, особенно при ограниченной лементарных посылок сигналов ретения яв ования. предложенн опер ежен иминаторов включены тые преобр ттуду опорн приведенаяется повышен т ом устройстве межие и отставание и входами фильтровпрямо и обратно 15 азователи фазового ого импульса.блок-схема устройства.Входные клеммы 1 устройства соединены со 20 входом фазовых дискриминаторов 2, выходы опережение которых подключены к прямо пропорциональным преобразователям 3 фазовый сдвиг - амплитуда последующего опорного импульса, а выходы отставание - к об ратно пропорциональным преобразователям 4 фазовый сдвиг - амплитуда последующего опорного импульса. Выходы управления фазовых дискриминаторов 2 соединены с выходом триггера 5, Выходы преобразователей 3 Зо Известно устформацией скоинформация оляется из одногканала,Недостаткомся его неточносдлительности эв подканалах.Целью изобточности фазирДля этого вду выходамифазовых дискрсоответственнопропорциональсдвига в амплуаНа чертеже и 4 подключены к фильтрам 6 и 7. Выходы фильтров 6 и трактов опережение соединены со входом сумматора 8, а выходы фильтров 7 трактов отставание - со входом сумматора 9.Выходы сумматоров 8 и 9 подключены ко входам двухканального избирательного усилителя-интегратора 10, выходы которого соединены со входом формирователя 11 импульсов подстройки.Вход управления формирователя 11 соединен с одним из выходов задающего генератора 12, Другой выход генератора 12 и выходы формирователя 11 подключены ко входам управляемого делителя 13, выход которого соединен со входом триггера 5 и выходной клеммой 14 устройства.На входную клемму 1 поступает входной сигнал, который проходит на фазовый дискриминатор 2, Дискриминатор 2 различает положение входных импульсов относительно опорного напряжения триггера 5, и если знакоперемена входного сигнала опережает опорное напряжение не более чем на половину тактового периода, то дифференциал от знакоперемены поступит на вход прямо пропорционального преобразователя 3.Если знакоперемена входного сигнала отстает от фазы опорного напряжения не более чем на половину тактового периода, то диф678/17 Тираж 473зобретеии 11 и откргятиш ири С7 К, 1 аугиская иабд. 4/5 1 ад.293 ЗакаЦНИИПИ Комитета по делахМоска Подписноес Министров ССС 1 Типография, ир. Сапунова, 2 ференциал от зна копер емены поступит на обратно пропорциональный преобразователь 4. Управление преобразователями 3 и 4 осуществляется с различных плеч триггера 5.С выхода преобразователя 3 амплитудно- модулированные импульсы поступают па фильтр б и возбуждают в пем колебательное напряжение частотой Рь Лмплитудно-модулированные импульсы с преобразователя 4 поступают па фильтр 7 со сдвигом па половину тактового периода относительно импульсов с преобразователя 3. Фильтр 7 настроен на частоту РТаким образом, в трактах опережение обоих подканалов с выхода фильтров б синфазные колебательные напряхкеп 11 я поступают на сумматор 8, а колебательпые напряжения с выхода фильтров 7 - на сумматор 9. 11 апряжения с выходов сумматоров 8 и 9 подаются на двухканальный избирательный усилительпнтегратор 10, напряжения с выходов которого управляют работой формирователя 11 импульсов подстройки. Частота и знак импульсов подстройки, поступающих на управляемый делитель 13, определяются знаком и степенью несимметрии напряжений с усилителя-интегратора 10.Частота импульсов подстройки не зависитот количества знакоперемен во входном сиг нале, и определяется только разностью интегральных значений фазовых сдвигов между трактами опережение и отставанпе всех подканалов. Пр едм ет изобретенияУстройство фазирования для цифровых систем с последовательно-параллельной трансформацией скорости передачи, содержащее в каждом подканале фазовый дискриминатор, 15 два фильтра, а в групповой части - два сумматора, двухканальный избирательный усилитель-интегратор, формирователь импульсов подстройки, управляемый делитель и задающий генератор, отлта)ош,ееся тем, что, с 20 целью повышения точности фазпрованпя, между выхода ми опережение и отставанпе фазовых дискриминаторов и входамп фильтров соответственно включены прямо и обратно пропорциональные преобразователи фазо вого сдвига в амплитуду опорного импульса.

СмотретьЗаявка

1293261

Г. А. Полиевский, В. А. Воронцов

МПК / Метки

МПК: H04L 7/033

Метки: последовательно-параллельной, систем, трансформацией, фазирования, цифровых

Опубликовано: 01.01.1971

Код ссылки

<a href="https://patents.su/2-295204-ustrojjstvo-fazirovaniya-dlya-cifrovykh-sistem-s-posledovatelno-parallelnojj-transformaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство фазирования для цифровых систем с последовательно-параллельной трансформацией</a>

Предыдущий патент: Устройство преобразования телеграфных посылок в импульсные сигналы

Следующий патент: Координатная автоматическая телефонная станция

Случайный патент: Станок для изготовления коленчатых валов