Кодер кода 3в2

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1244803

Авторы: Кордонский, Котиков

Текст

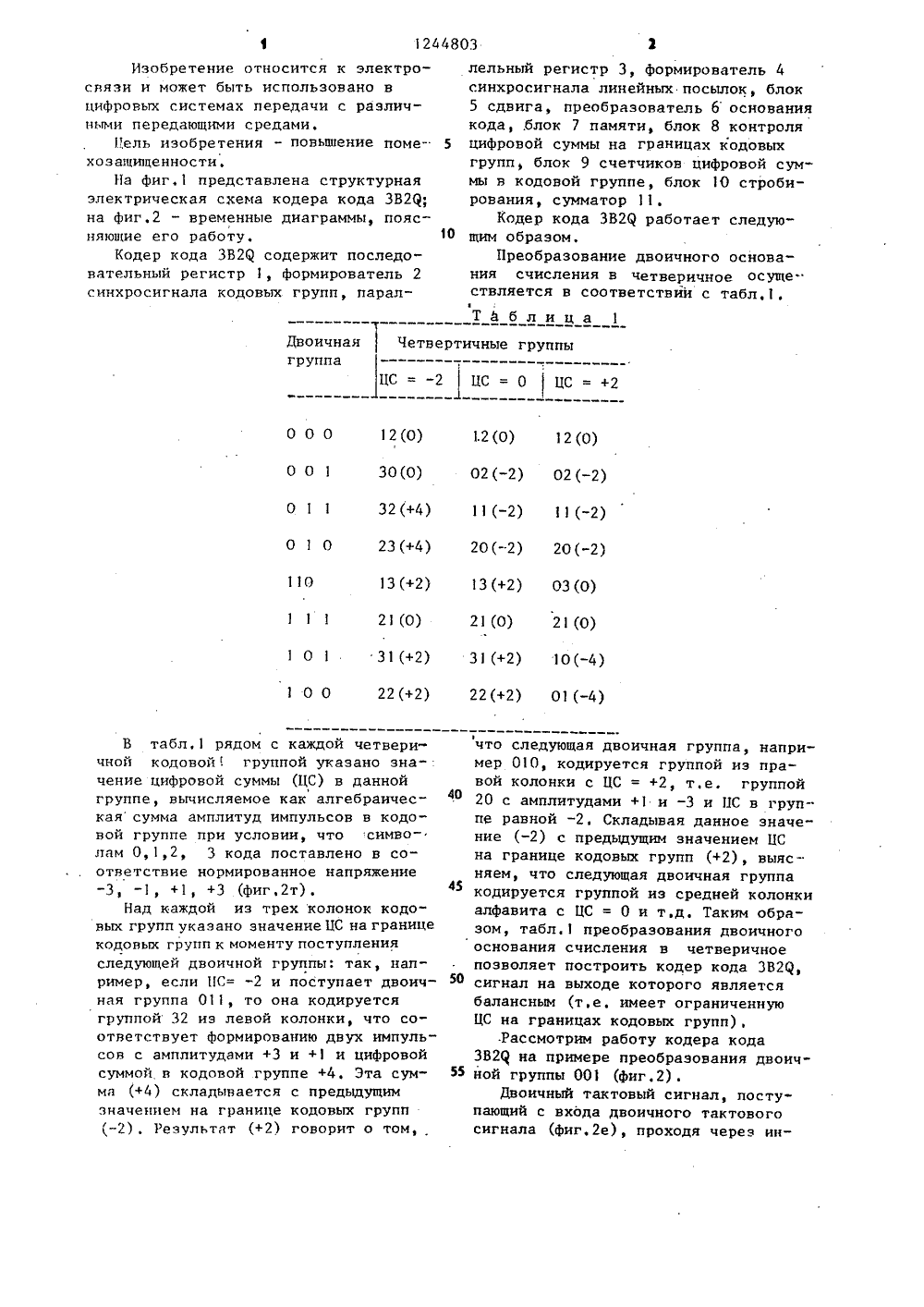

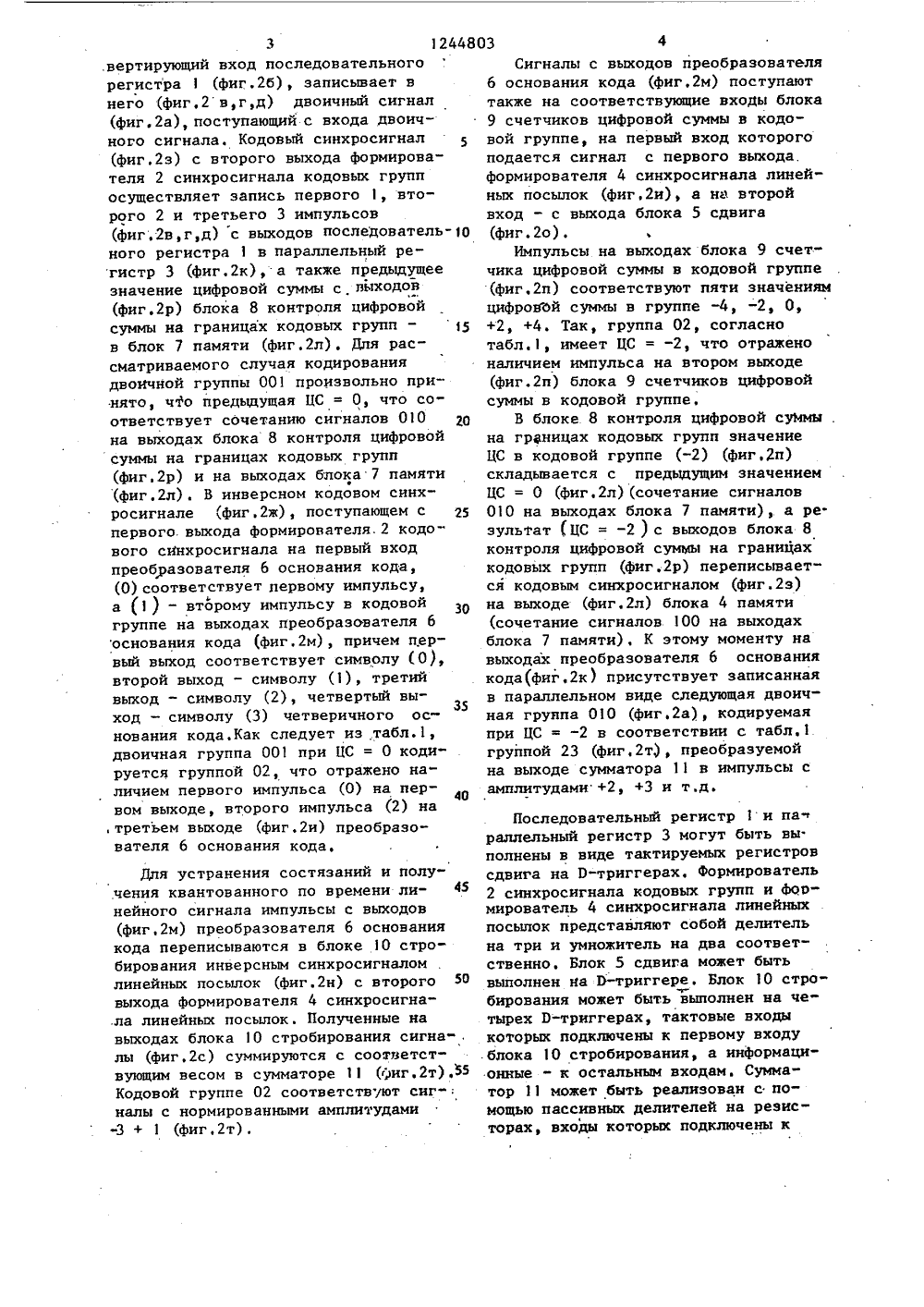

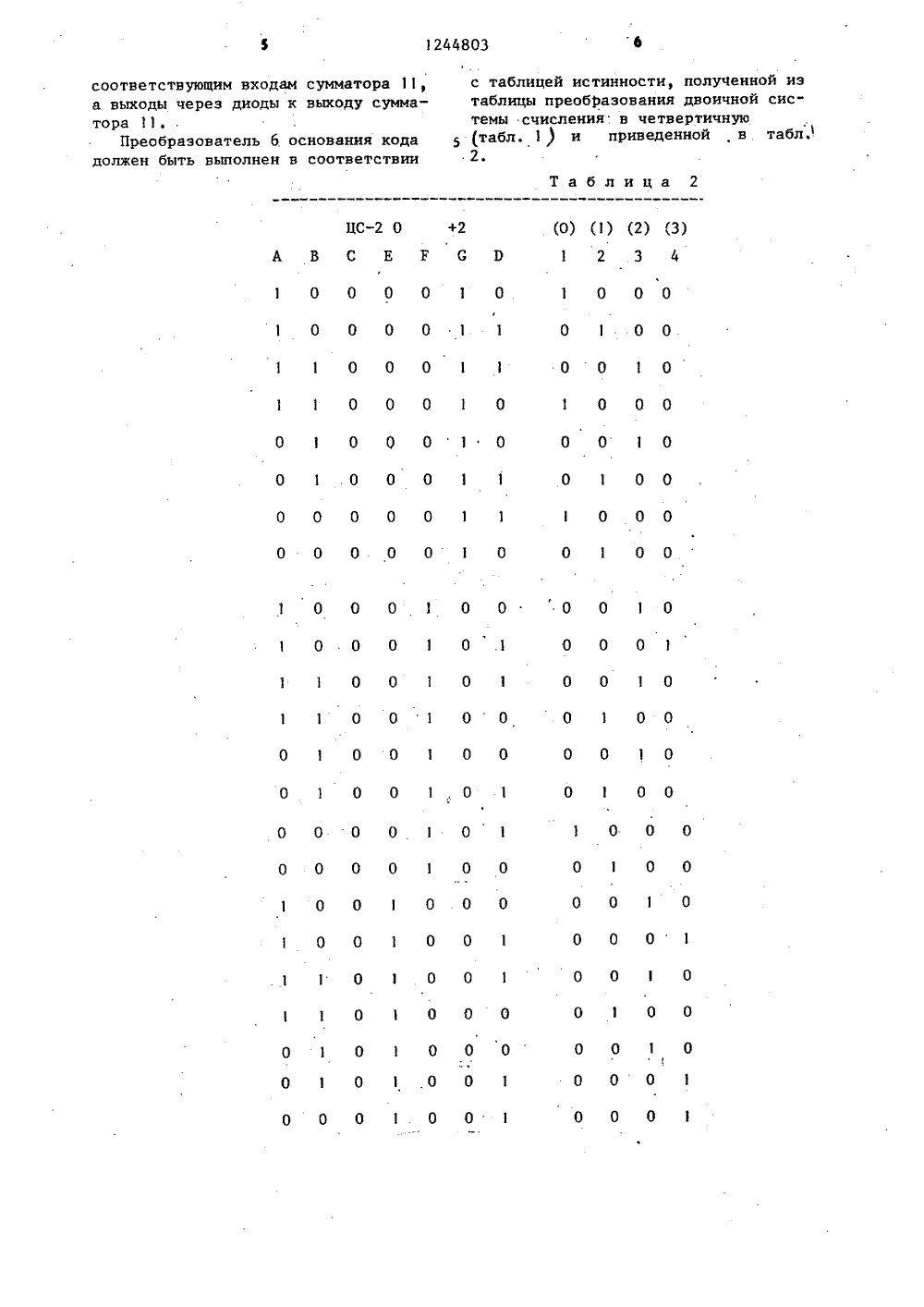

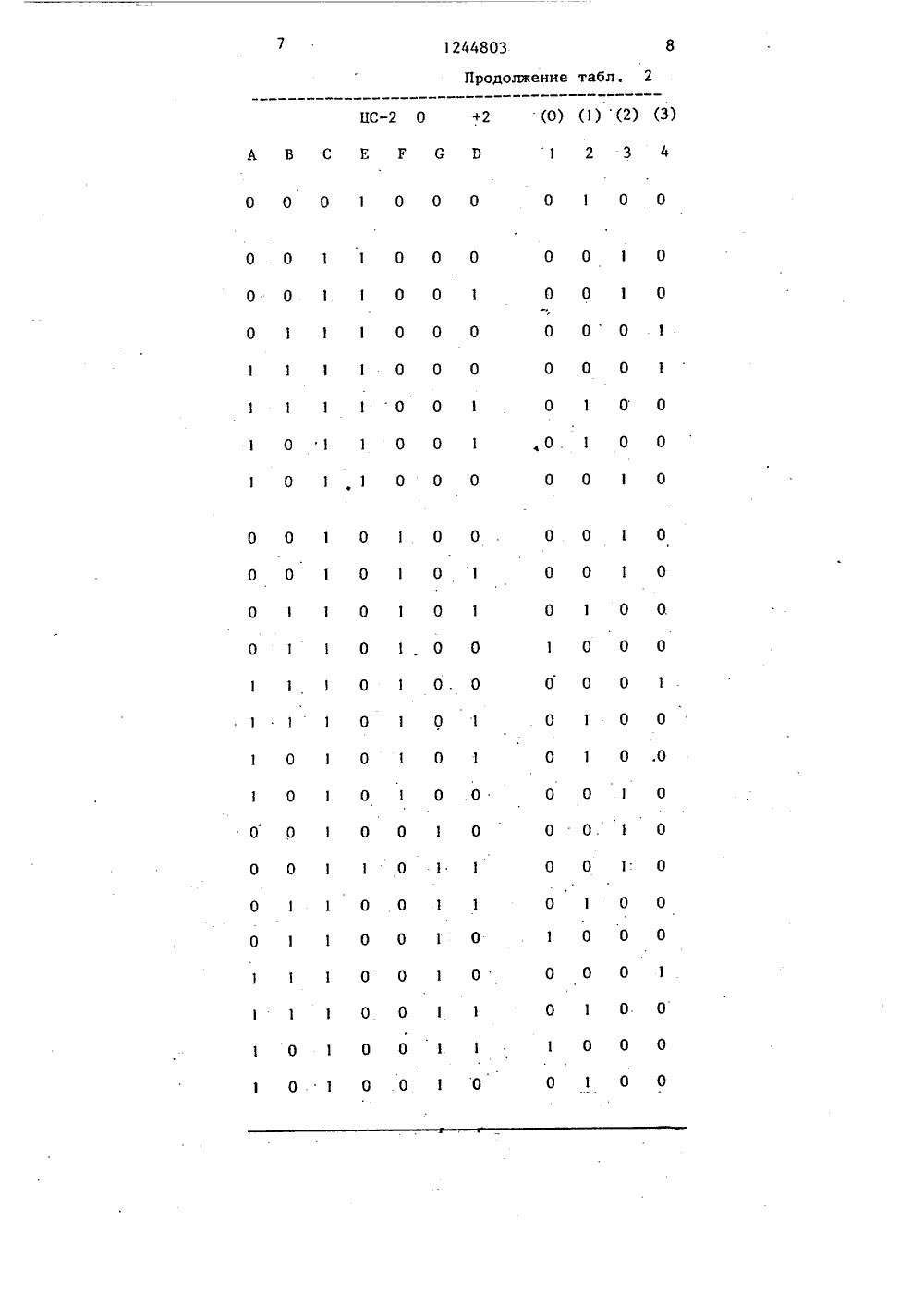

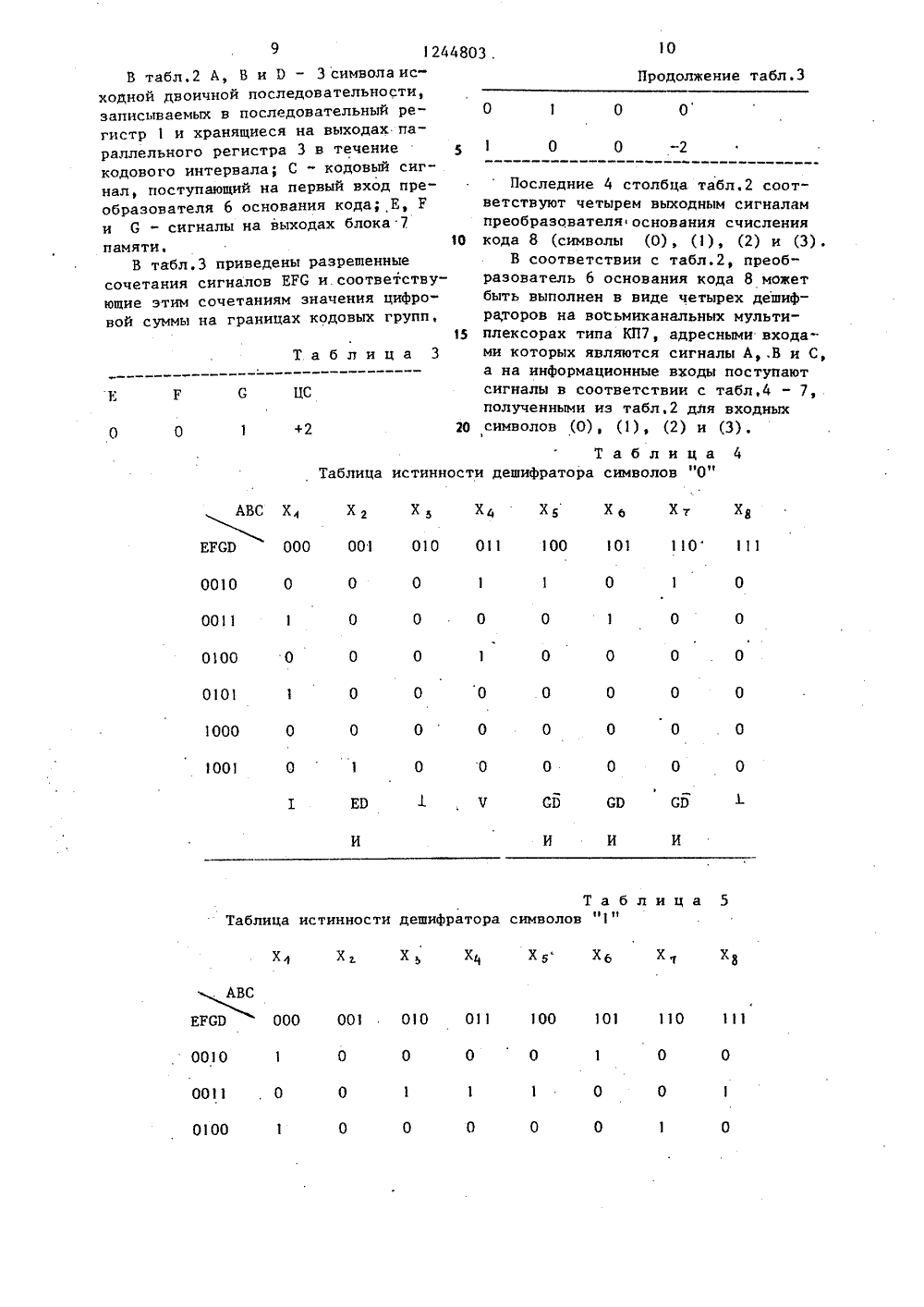

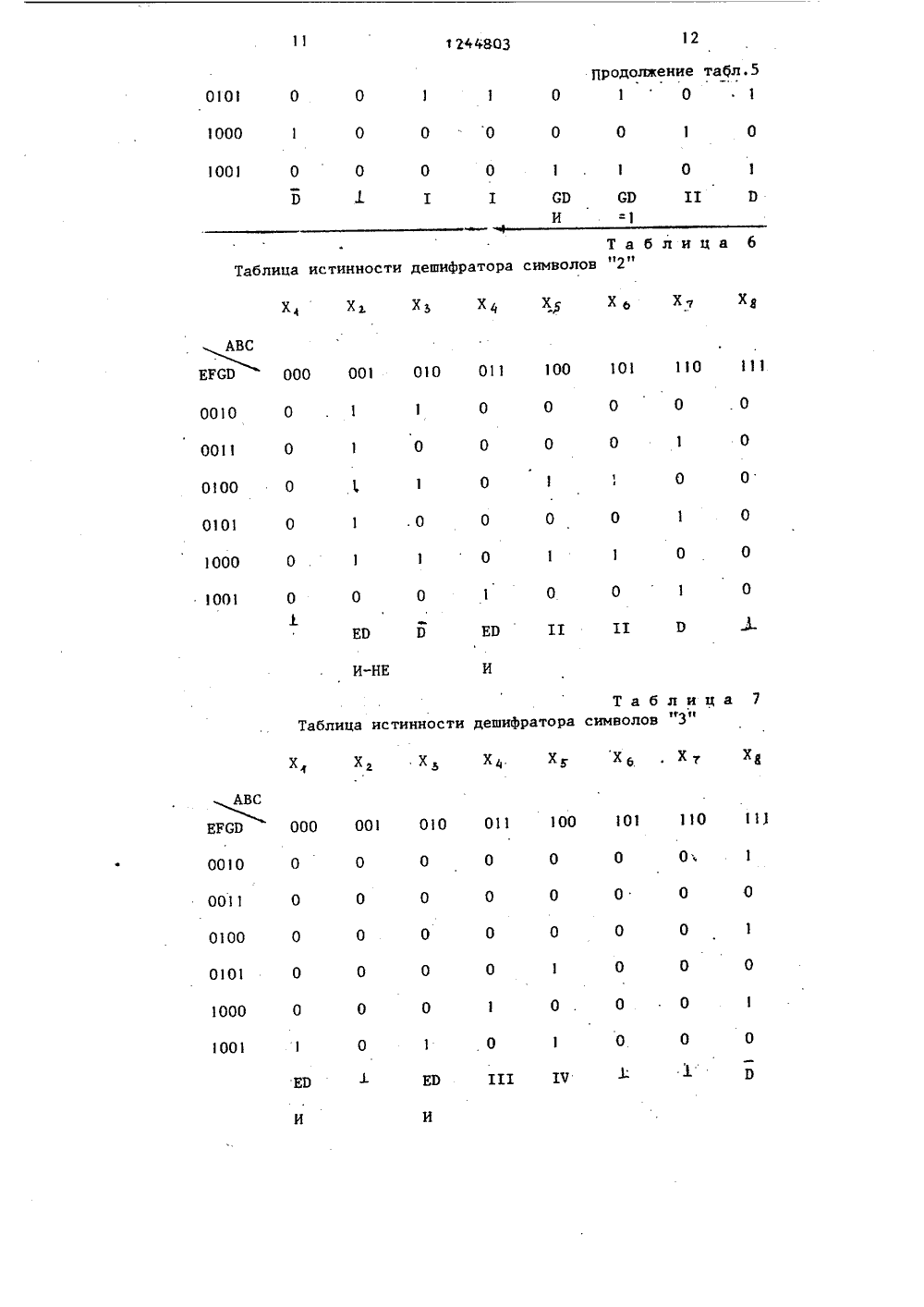

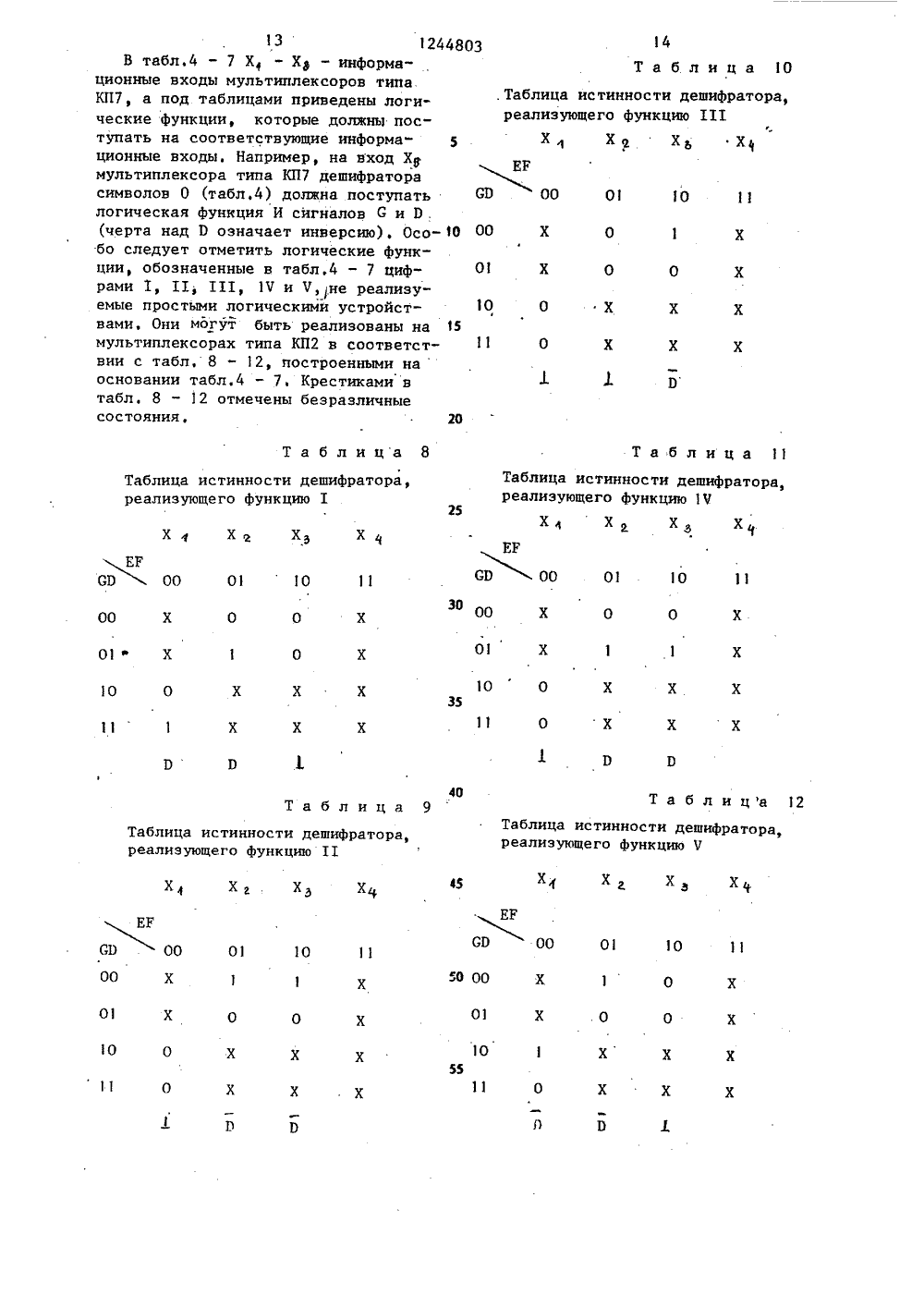

09) ИИ СОЮЗ СОВЕТСНИХ(59 4 Н 04 1 5/00 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОбРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ ИЗОБРЕТЕНИЯ и,., ,13 К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ,56) Левин Л.С., Плоткин Х,А, Цифровые системы передачи информации, М.: Радио и связь, 1982, с.192, 95.Авторское свидетельство СССР В 688082, кл Н 04 1 5/00, 1976 (54) КОДЕР КОДА ЗВ 2 Я.(57) Изобретение относится к злектросвязи, Повыиается помехозащищенность. Устройство содержит последовательный регистр (Р) 1, формирователь синхррсигнала кодовых групп 2, параллельный РЗ, формирователь синхросигнала линейных посылок 4, блок сдвига 5, .преобразователь основания кода 6,блок памяти 7, блок контроля (БК)8 цифровой суммы на границах кодовых групп, блок счетчиков (БС) 9 цифровой сЬмы в кодовой группе, блок стробирования 10 и сумматор 11; В устройстве осуществляется преобразование двоичного основания счисления в четвертичное в соответствии с табл,1. Табл 1 позволяет построить . устройство, сигнал на выходе которого является балансным, т.е. имеет ограниченную цифровую сумму на границах кодовых групп. Цель достигается введением Р 1 и 3, блока сдвига 5, блока памяти 7, БК 8, БС 9 и блока стро-бировання 10, Приведены табл, истин- В ности, в соответствии с которыми выполнены преобразователь 6, БС 9 и БК 8. 2 ил, 22 табл. С:20 244803 Таблица 16 Таблица истинности мультиплексора, подсчитывающего циФровую сумму (0) Ха Ху У, 3, ,000 001 010 011 100 1012 Ф б 8 110 110001 Х Х Х Х Х 10100 0 Х Х . Х Х Хгу10010 0 Х Х Х Х Х Х Х Х 01000Х 0 . 0 Х Х Х 00100 Х 1 0 Х 0 Х.Х Х 00010 Х 0 3 Х 0 Х Х 00001.Х 0 0 Х 1Х Таблица 17 Таблица истинности мультиплексора, подсчитывающего цифровую сумму (+2) Х 33 Х Х Х Х Х Х 11000 0 10100 1 Х Х Х Х Х Х Х 10010 0 Х Х Х Х Х ХХ Х Ю Х 01000 Х . О . 0 Хс Х 00010 Х 1 0 Х 0 Х Х Х 0 Х . Х 00001 Х 73 УУ Ъ 324 6 Э21 124480322Таблица 18Таблица истинности мультиплексора, подсчитывающего цифровую сумму (+4)х Х 2 х х, Х х, Х х.М ф ОООО 001 010 01 ОО 101 110 у Ъек11000 0 Х Х Х ". Х Х Х Х Х Х Х Х Х Х Х Х 1000 0 Х Х 10010 1 Х Х О 000 Х 0 0 Х Х Х Х Х Х Х Х 00100 Х 0 .0 . Х 0 Х Х 00010 Х 0 0 Х О Х Х Х Х 1 0 Х 0 Х ХТе 00001 выполнен в соответствии с табл,9, полученной ив таблицы преобразования двоичной системы счисления в четверичную 1 (табл,1),Таблица 19 Таблица истинности блока контроля цифровойсуммы на .гранИцах кодовых групп(-4) (-2) (0) (+2) (14) .-2 0 +2 Е: Р С Е,0 0 0 0 1 1 0 0 0 1 0 0 0 О 00 01 0 0 0 О 1 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 0 . 0 0 0 1 0 0 1 0 0 1 О 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 1 0 01 0 0 В табл.14 - 18 Х - Х - информа" ционные входы мультиплексоров типа КП 7, а УФ У Уу - адресные входы.Блок 8 контроля цифровой суммы на границах кодовых групп должен быть 1 0 0 0 1 0 0 0 1 1 0 О 0 1 0 0 0 1Таблица истинности мультиплексора дляцифровой суммы (-2) Х Х Х Х 1 .Х Хб Хе Хз 000 001 010 011гг,г,г, г60 101 110 10000 . Х 1 Х Х Х Х Х Х Х Х 01000 Х 0 1 Х Х Х Х 0000 Х 0 0 Х 1 Х Х Х 0 Х 0 Х Х Х 00010 Х Х О Х Х Х Х00001 Х гг%Таблица 21Таблица истинности мультиплексора дляцифровой суммы (0) Х ХО Ха Хч Хр Ха Х Ху 000 011 010 011 100 01 110111ггг, Е 4 Е,. Х Х 0 Х Х Х Х Х Х 1 0 Х Х Х Х Х0 1 К 0 Х Х Х Х 0 Х 1 Х Х 10000 01000 Х 00100 00010 Х 00001Х Х Х Х 0 Х Хг, г, г.+ Т а.б л и ц а 22Таблица истинности мультиплексора дляцифровой суммы (+2) Х 1 Ха Х Х 1 Х Хб Ху Х000 001 010 011 100 101 110 111 ЕРС 10000 Х 0 Х . Х Х Х Х Х 23 1244803 24В нем происходит суммирование зна- табл.9, блок 8 контроля цифровойчения предыдущей цифровой суммы с вы- суммы на границах кодовых групп моходов блока 7 памяти (Е Г С, табл.19) жет быть выполнен в вице дешифратораи значения цифровой суммы в данной на трех. мультиплексорах типа КП 7,кодовой группе с выходов блока 9 таблицы истинности которых полученысчетчиков цифровой суммы (г, гаО из табл. 19 и приведены вг, г Ех), В соответствии с табл. 20-22,Таблица 2026 1244803 Продолжение табл.22 01000 Х 0 0 Х Х Х Х 00100 Х0 Х 0 Х Х 00010 Х Х 1 Х 0 Х Х Х Х 00001 Х Х Х Х 1 Х Х 15 20 Блок 7 памяти может быть выполнен на трех Р-триггерахинформационные входы которых соединены с входами блока 7 памяти, а тактовые входы - с входами, подключенными к второму выходу формирователя 4 синхросигнала кодовых групп. Формула изобретения Кодер кода ЗВ 2 Я, содержащий сумматор и формирователь. синхросигнала ко довых групп, выход которого подключен к входу формирователя синхросигнала линейных посылок и первому входу преобразователя основания кода, причем вход формирователя. синхросигнала кодовых групп является входом двоич-. ного тактового сигнала кодера, выходом которого является выход сумматора, о т л и ч а ю щ е е с Й тем, что, с целью повышения помехозащищен" ности,. в него введены последователь ный регистр, блок стробирования, блок счетчиков цифровой суммы в кодовой группе, блок контроля цифровой суммы на границах кодовых групп, блок памяти, параллельный регистр и блок сдви- ф га, к первому входу которого подключен первый выход формирователя синхросигнала кодовых групп, второй выход которого подключен к первым входамблока памяти и параллельного регистра, к остальным входам которого подключены выходы последовательного регистра, прямой и инвертирующий тактовыйвходы которого являются соответственновходом двоичного сигнала и входом двоич"ного тактового сигнала, при этом первый выход формирователя синхросигнала линейных посылок подключен к первому входу блока. счетчиков цифровойсуммы в кодовой группе, к второмувходу которого подключен выход блокасдвига, к второму входу которого ипервому входу блока стробированияподключен второй выход формирователясинхросигнала линейных посылок, авыходы параллельного регистра подключены к второму, третьему и четвертомувходам преобразователя основания кода, выходы которого через блок: стробирования подключены к входам сумматора и через последовательно соединенные блок счетчиков цифровой суммыв кодовой группе, блок контроля цифровой суммы на границах кодовых группи блок памяти к пятому, шестому иседьмому входам преобразователя основания кода и шестому, седьмому и восьмому входам блока контроля цифровойсуммы на границах кодовых групп,1244803 Циткина еда аказ 392 Тираж 62 НИИПИ Государственного к по делам изобретений и 13035, Москва, Ж, Рауш244803 Двоичная Четвертичные группы группа ЦС = -2 ЦС = 0 ЦС = +2 12 (О) 1.2 (О) 000 001 12 (О) 30 (О) 02 (-2) 02 (-2) 1 1 (-2) 1 1 (-2) 32 (+4) 011 23 (+4) 20 (- 2) 20 (-2)13 (+2) 13 (+2) 03 (О) 010 11 О 21 (О) 21 (О) 21 (0) 31 (+2) 31 (+2) 1 О (-4) 101 100 22 (+2) 22 (+2) 01 (-4) Изобретение относится к электросвязи и может быть использовано вцифровых системах передачи с различными передающими средами,Цель изобретения - повышение помехоэащищенности,На фиг,1 представлена структурнаяэлектрическая схема кодера кода ЗВ 2на фиг,2 - временные диаграммы, поясняющие его работу.Кодер кода ЗВ 2 Я содержит последовательный регистр 1, формирователь 2синхросигнала кодовых групп, паралВ табл,1 рядом с каждой четверичной кодовойгруппой указано зна" чение цифровой суммы (ЦС) в данной группе, вычисляемое как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что символам 0,1,2, 3 кода поставлено в соответствие нормированное напряжение -3, -1, +1, +3 (фиг,2 т).Над каждой из трех колонок кодовых групп указано значение ЦС на границе кодовых групп к моменту поступления следующей двоичной группы: так, нап" ример, если ПС= -2 и поступает двоичная группа 011, то она кодируется группой 32 из левой колонки, что соответствует формированию двух импульсов с амплитудами +3 и +1 и цифровой суммой в кодовой группе +4, Эта сумма (+4) складывается с предыдущим значением на границе кодовых групп (-2). Результат (+2) говорит о том,лельный регистр 3, формирователь 4 синхросигнала линейных посылок, блок 5 сдвига, преобразователь 6 основания кода, .блок 7 памяти, блок 8 контроля цифровой суммы на границах кодовых групп, блок 9 счетчиков цифровой суммы в кодовой группе, блок 10 стробирования, сумматор 11.Кодер кода ЗВ 2 Я работает следующим образом.Преобразование двоичного основания счисления в четверичное осуще" ствляется в соответствии с табл,1, 1Таблица 1 1что следующая двоичная группа, например 010, кодируется группой из правой колонки с ЦС = +2, т.е, группой4 О 20 с амплитудами +1 и -3 и ЦС в группе равной -2. Складывая данное значение (-2) с предыдущим значением ЦСна границе кодовых групп (+2), выясняем, что следующая двоичная группакодируется группой из средней колонкиалфавита с ЦС = 0 и т.д, Таким образом, табл,1 преобразования двоичногооснования счисления в четверичноепозволяет построить кодер кода ЗВ 2 Я,50 сигнал на выходе которого являетсябалансным (т.е. имеет ограниченнуюЦС на границах кодовых групп),.Рассмотрим работу кодера кодаЗВ 2 Ц на примере преобразования двоич 55 ной группы 001 (фиг.2) .Двоичный тактовый сигнал, поступающий с входа двоичного тактовогосигнала (фиг.2 е), проходя через ин3 12448 .вертирующий вход последовательного регистра 1 (фиг.2 б), записывает в него (фиг,2 в,г,д) двоичный сигнал (фиг.2 а), поступающий с входа двоичного сигнала. Кодовый синхросигнал (фиг.2 з) с второго выхода формирователя 2 синхросигнала кодовых групп осуществляет запись первого 1, второго 2 и третьего 3 импульсов (фиг.2 в,г,д) с выходов последователь-О ного регистра 1 в параллельный регистр 3 (фиг,2 к), а также предыдущее значение цифровой суммы с выходов (фиг.2 р) блока 8 контроля цифровой суммы иа границах кодовых групп - 5 в блок 7 памяти (фиг,2 л). Для рассматриваемого случая кодирования двоичной группы 001 произвольно принято, что предыдущая ЦС = О, что соответствует сочетанию сигналов 010 0 на выходах блока 8 контроля цифровой суммы на границах кодовых групп (фиг.2 р) и на выходах блока 7 памяти (фиг.2 л). В инверсном кодовом синхросигнале (фиг.2 ж), поступающем с д первого. выхода формирователя. 2 кодового синхросигнала на первый вход преобразователя 6 основания кода, (0) соответствует первому импульсу, а (1 ) - второму импульсу в кодовой группе на выходах преобразователя 6 основания кода (фиг.2 м), причем первый выход соответствует символу (0), второй выход - символу (1), третий выход - символу (2) четвертый выФ35 ход - символу (3) четверичного основания кода.Как следует из табл.1, двоичная группа 001 при ЦС = 0 кодируется группой 02, что отражено наличием первого импульса (0) на пер 40 вом выходе, второго импульса (2) на , третьем выходе (фиг,2 и) преобразователя 6 основания кода. Последовательный регистр 1 и па раллельный регистр 3 могут быть вы. полнены в виде тактируемых регистров сдвига на Р-триггерах. Формирователь 2 синхросигнала кодовых групп и Формирователь 4 синхросигнала линейных посылок представляют собой делитель на три и умножитель на два соответственно. Блок 5 сдвига может быть выполнен на П-триггере, Блок 10 стробирования может быть выполнен на четырех П-триггерах, тактовые входы которых подключены к первому входу блока 1 О стробирования, а информационные - к остальным входам. Сумматор 11 может быть реализован с помощью пассивных делителей на резисторах, входы которых подключены к Для устранения состязаний и получения квантованного по времени линейного сигнала импульсы с выходов(фиг,2 м) преобразователя 6 основаниякода переписываются в блоке 1 О стробирования инверсным синхросигналомлинейных посылок (фиг.2 н) с второго 50выхода формирователя 4 синхросигна".ла линейных посылок. Полученные навыходах блока 10 стробирования сигна-,лы (фиг,2 с) суммируются с соответствующим весом в сумматоре 11 (уиг.2 т).55Кодовой группе 02 соответствуют сиг-:налы с нормированными амплитудами-3 + 1 (фиг,2 т),03 4Сигналы с выходов преобразователя6 основания кода (фиг,2 м) поступаюттакже на соответствующие входы блока9 счетчиков цифровой суммы в кодовой группе, на первый вход которогоподается сигнал с первого выхода.формирователя 4 синхросигнала линейных посылок (фиг,2 и), а на второйвход - с выхода блока 5 сдвига(фиг.2 о),ЪИмпульсы на выходах блока 9 счетчика цифровой суммы в кодовой группе(фиг.2 п) соответствуют пяти значениямцифровой суммы в группе -4, -2, О,+2, +4. Так, группа 02, согласнотабл.1, имеет ЦС = -2, что отраженоналичием импульса на втором выходе(фиг.2 п) блока 9 счетчиков цифровойсуммы в кодовой группе,В блоке 8 контроля цифровой суммы .на границах кодовых групп значениеЦС в кодовой группе (-2) (фиг.2 п)складывается с предыдущим значениемЦС = 0 (фиг.2 л)(сочетание сигналов010 на выходах блока 7 памяти), а ре.эультат ЦС = -2 ) с выходов блока 8контроля цифровой суммы на границахкодовых групп (фиг,2 р) переписывается кодовым синхросигналом (фиг.2 з)на выходе (фиг.2 л) блока 4 памяти(сочетание сигналов 100 на выходахблока 7 памяти), К этому моменту навыходах преобразователя 6 основаниякода(фиг.2 к) присутствует записаннаяв параллельном виде следующая двоичная грунпа 010 (фиг.2 а), кодируемаяпри ЦС = -2 в соответствии с табл,1группой 23 (фиг,2 т), преобразуемойна выходе сумматора 11 в импульсы самплитудами +2, +3 и т.д.1244803 с таблицей истинности, полученной из таблицы преобразования двоичной системы счисления в четвертичную (табл. 1 ) и приведенной в табл, 2. Таблица 2 ЦС0 +2(0 0 00 0 0 1 0 0 0 1 . 0 0 1 соответствующим входаи сумматора 11, а выходы через диоды к выходу сумматора 11,Преобразователь 6 основания кода должен быть выполнен в соответствии 1 0 0 0 00 0 0 0 1 0 1 0 0 0 0 О 1 0 0 0 00 0 1 0 0 1 0 0 0 0 1 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 01 0 0 1 0 00 010 4803,Продолжение табл.З 0 0 0 5 0 0 -2 Таблица 3 С ЦС 1 +2 0 Таблица 4Таблица истинности дешифратора символов "0" Х Х 4Х Хь Хт ХВ АВС Хл Х 2ЕРСП 000 001 010 011 0 1 0 0 100 101 1 0 0110 111 1 0 0 0010 0 0011 0 0 0 0 0 0100 0 0101 1 1000 0 1001 0 0 0 0 0 0 0 0 0 0 0 0 . 0 0 0 0 С 0 СР 0 0 0 0 Е 0 Таблица 5Таблица истинности дешифратора символов "1" Х ХБ Х Х Х ХХ, Х,АВСЕРШ 000 001 010 011 100 101 110 111 0 0 0 0010 1 0 0 0011 , 0 0 0 0 0 0 0 0100 1 0 9124В табл.2 А, В и Э - 3 символаисходнай двоичной последовательности, записываемых в последовательный регистр 1 и хранящиеся на выходах параллельного регистра 3 в течение кодового интервала; С " кодовый сиг" нал, поступающий на первый вход преобразователя 6 основания кода; Е, Р и С - сигналы на выходах блока 7 памяти,В табл.З приведены разрешенные сочетания сигналов ЕРС и.соответствующие этим сочетаниям значения цифровой суммы на границах кодовых групп,Последние 4 столбца табл,2 соответствуют четырем выходным сигналампреобразователяоснования счисления1 О кода 8 (символы (О), (1), (2) и (3) .В соответствии с табл.2, преобразователь 6 основания кода 8 можетбыть выполнен в виде четырех дешифраторов на воьмиканальных мульти 15 плексорах типа КП 7, адресными входами которых являются сигналы А,.В и С,а на информационные входы поступаютсигналы в соответствии с табл,4 - 7,полученными из табл,2 для входных2 О симв олов (0), (1 ), (2 ) и (3),СЭ СР 11 0И =1 Таблица 6и иТаблица истинности дешифратора символов 2 ХА ХА Хс ХХу Хо х,Хл АВСЕРЖ 000 001 010 011 100 101 110 1110 .0 0 0 1 0 0 О 0 0 0 0 О 0 0 0 0 0 0101 0 0 0 1000 0 1001 0 0 0 0 0 0 11 11 Э Е 0 Р И И-НЕ Таблица 7 и и Таблица истинности дешифратора символов 3Х . Х Х. Ху Хб, Ху Х АВСВВОО ООО ОО О 1 О О 11 100 101 0010 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1000 0 0 1001 1 0 0 0 1 р 0 ЕВ ЕЭ И 0010 0 0011 0 0100 0 001 0 0100 0 0101 0 0 0 1 0 0 . О.1 0 110 113 0, 1 0 0 0 1.0 0 0 0 1 О Х Х Х 11 Х Х Х П 13В табл.4 - 7 Х - Х - информационные входы мультиплексоров типа КП 7, а под таблицами приведены логические функции, которые должны поступать на соответствующие информа ционные входы, Например, на вход Х мультиплексора типа КП 7 дешифратора символов 0 (табл,4) должна поступать логическая функция И сигналов С и П . (черта над П означает инверсию). Осо- О бо следует отметить логические функции, обозначенные в табл.4 - 7 цифрами 1, 11, 111, 1 Ч и Ч,не реализуемые простыми логическими устройствами, Они могут быть реализованы на 15 мультиплексорах типа КП 2 в соответствии с табл, 8 - 12, построенными наосновании табл,4 - 7, Крестиками в табл8 - 12 отмечены безразличные состоянияТаблица истинности дешифратора,реализующего функцию 1 х х, х, х Таблица истинности дешифратора,реализующего функцию 11 Х, Х, Х, Х,.Таблица истинности дешифратора,реализующего функцию 111ФиХХ, Х, Х Таблица истинности дешифратора,реализующего функцию 1 Ч Таблица истинности дешифратора,реализующего функцию Ч ХХ Х, Х1244803 отражает появление группы 30, преобразуемой в импульсы с амплитудами +3,"3 с цифровой суммой в группе, равной нулю (наличие импульса на выходеблока счетчика цифровой суммы в кодовой группе 11, табл.13). В соответствии с табл.13, блок 9 счетчиков.цифровой суммы в кодовой группе может быть выполнен в виде дешифраторана пяти мультиплексорах тина КП 7,таблицы истинности которых приведеныв табл.14 - 18,1 аблицацифровой Таблица истинности блока счетчиковсуммы в кодовой группе Первый символ Второй символ У ь ат а 1 с( а Т.В-3 -1 +1 Ф 3 0 1 1 О 1 2 0 0 0 1 2 3 0 0 О 0 0 0 0 0 1 00 0 0 1 0 1 О 0 0 0 1 0 0 0 0 1 0 0 1 0 0 О 1 0 0 О 0 1 О 1 0 0О 0 0 0 0 0 0 1 0 0 0 0 0 1 О 0 0 1 0 0 0 1 О 0 0 О0 0 1 0 0 О 0 0 1 0 0 О 1 0 0 0 0 1 0 0 0В 1 О О 0 1 0 0 0 1 0 0 0 0 1 0 О Блок 9 счетчиков цифровой суммы в кодовой группе должен быть выполнен в соответствии с табл.3, полученной из таблицы преобразования двоичной системы счисления в четверичную 5 (табл.1), Символам кода О, 1, 2, 3 ставятся в соответствие сигналы с нормированнои амплитудой -3, -1, +1, +3, что отражено в табл.3. При подсчете цифровой суммы в кодовой груп-пе берется алгебраическая сумма амп литуд первого и второго символов. Например, первая строка в табл.13 0 0 О 1 0 0 0 1 0 1 0 0 0 1 0 0 0 О 1 0 О 0 1 0 О О 0

СмотретьЗаявка

3827227, 18.12.1984

ПРЕДПРИЯТИЕ ПЯ Р-6609

КОТИКОВ ИГОРЬ МИХАЙЛОВИЧ, КОРДОНСКИЙ БОРИС ШЛЕМОВИЧ

МПК / Метки

МПК: H04L 5/00

Опубликовано: 15.07.1986

Код ссылки

<a href="https://patents.su/15-1244803-koder-koda-3v2.html" target="_blank" rel="follow" title="База патентов СССР">Кодер кода 3в2</a>

Предыдущий патент: Устройство для передачи и приема сигналов синхронизации генераторного оборудования систем передачи с частотным разделением каналов

Следующий патент: Устройство для синхронного радиоприема частотно манипулированных сигналов

Случайный патент: Устройство для изготовления витого магнитопровода электрической машины