Процессор матричной вычислительной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1603395

Авторы: Бутузов, Садовникова, Хрусталев

Текст

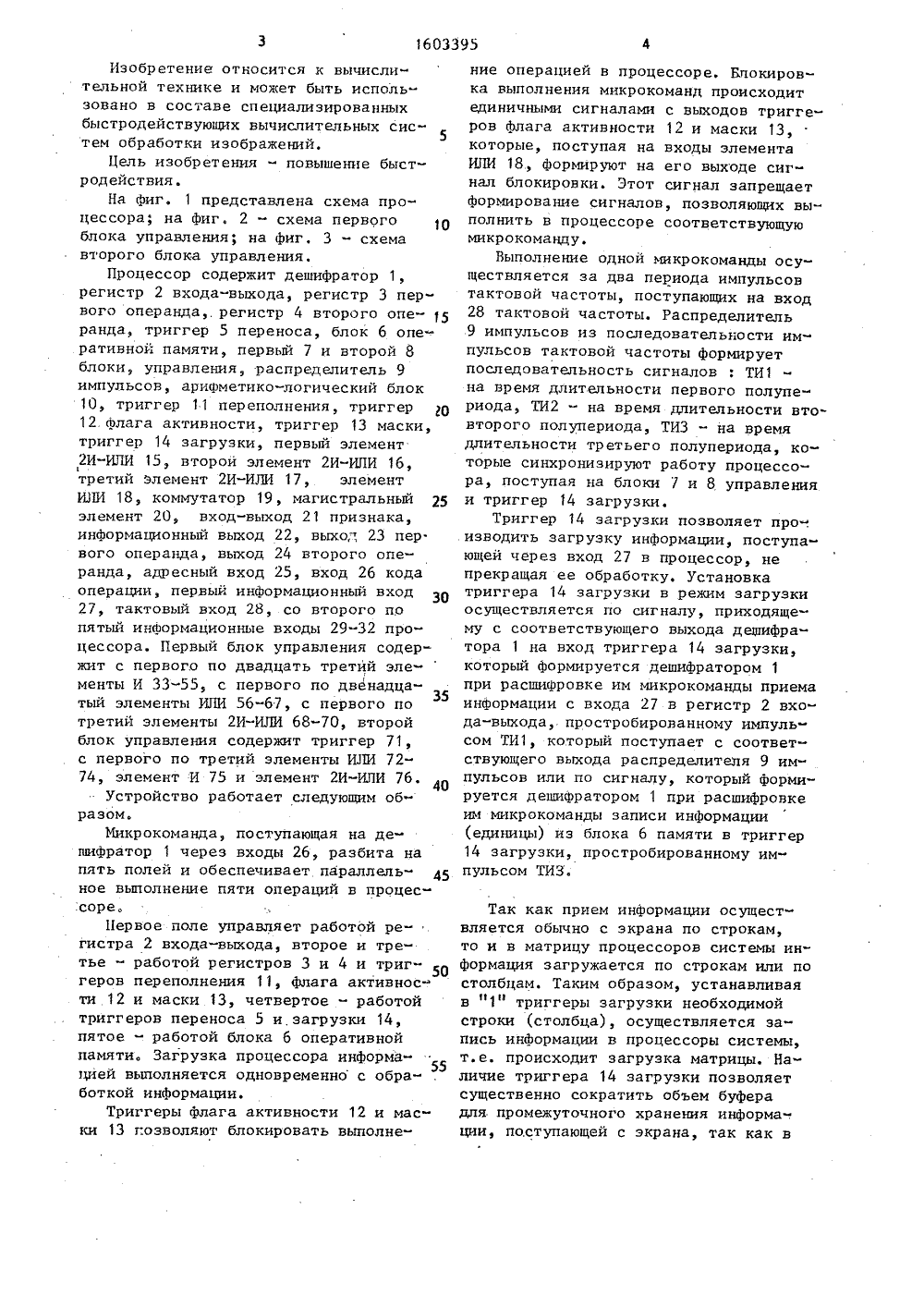

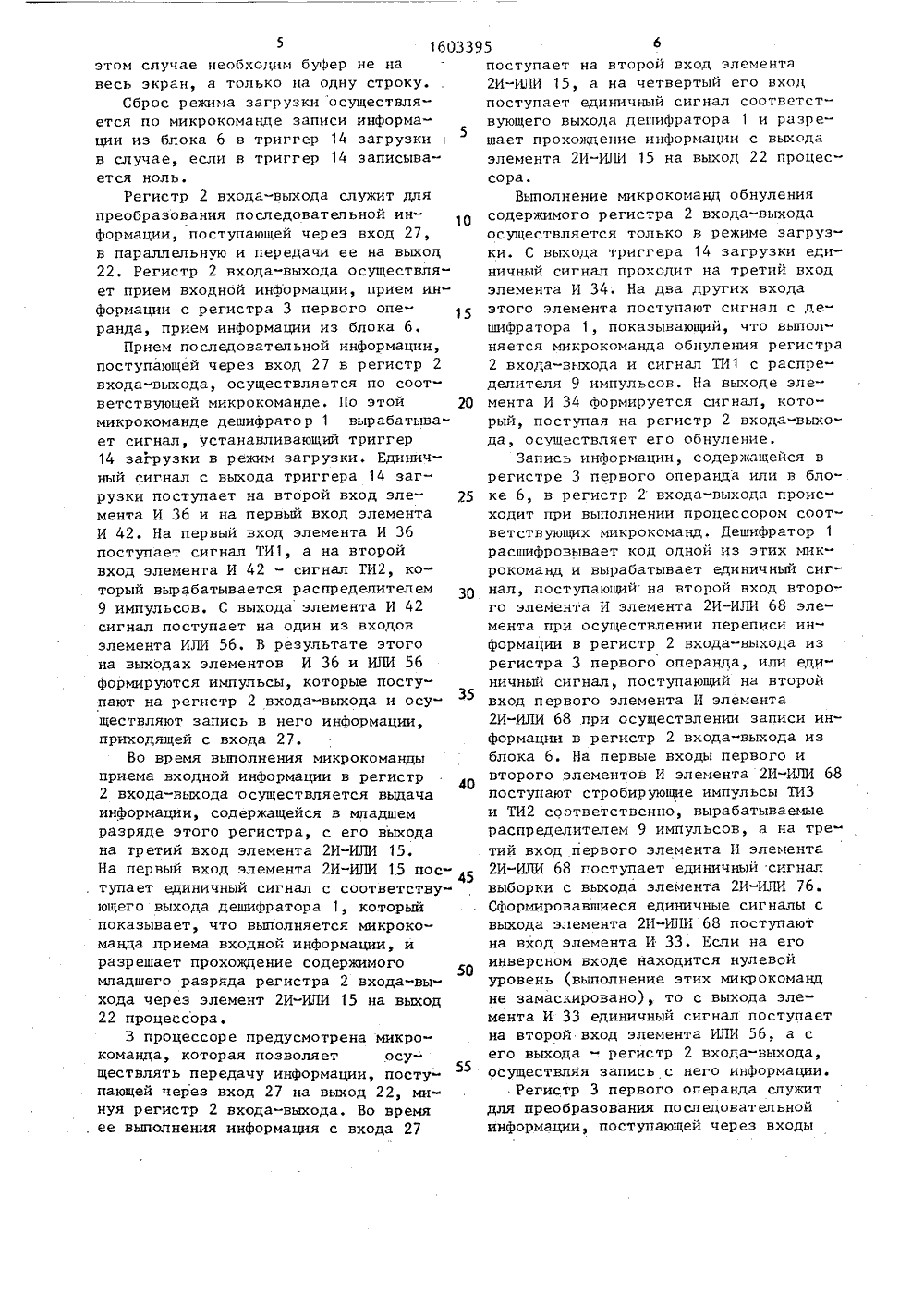

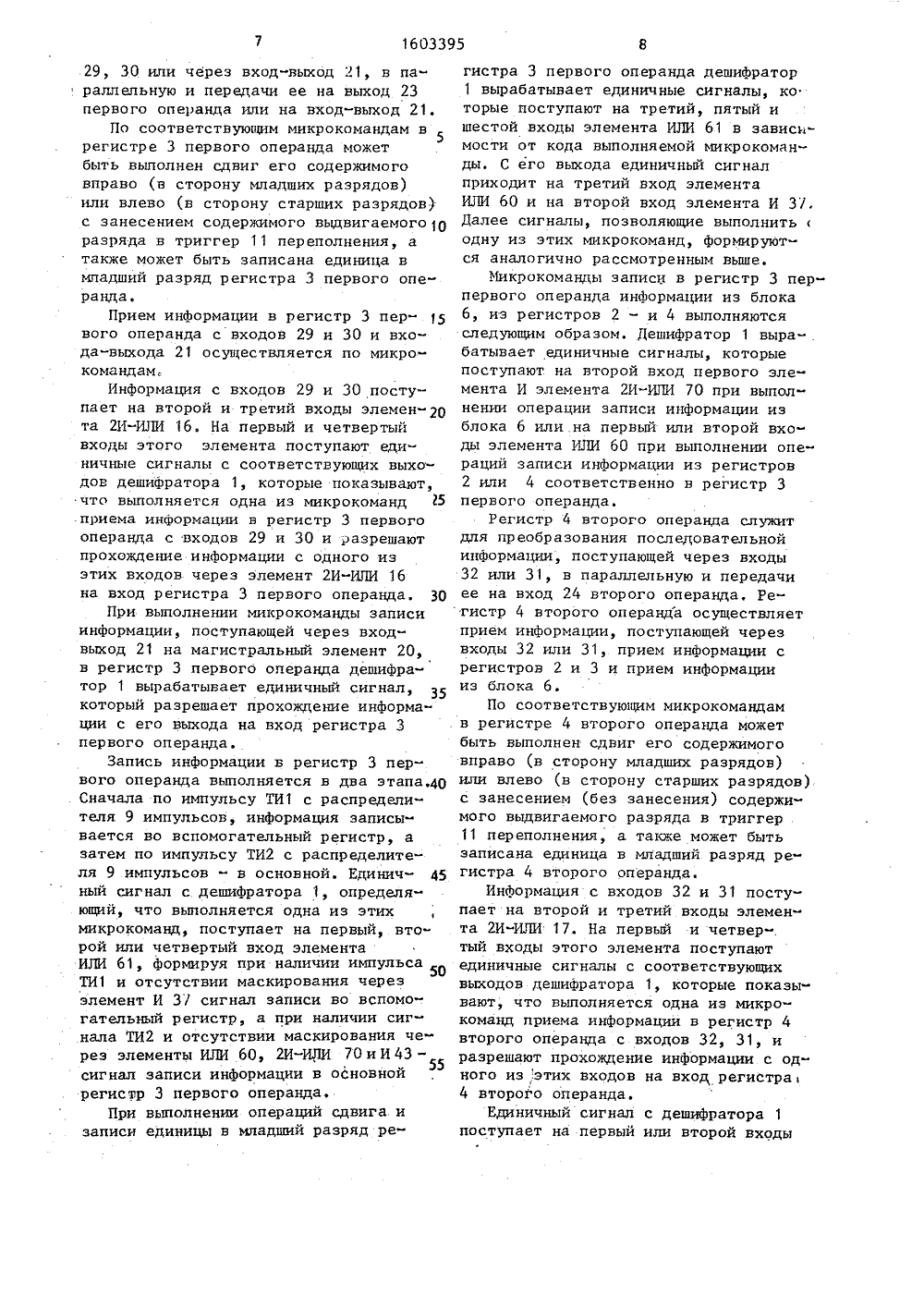

(51)5 С 06 Р 15/16 3 ЖВЗЯ 3ПАТЕЮКО - Т" Х"яЧЕ ИЯ иьлио г ОПИСАНИЕ ИЗОБРЕТЕНИЯ ВТОРСКОМУ СВ ЕПЬСТВ талев ды. юй е(57) Изобртельной те ОР МАТРИЧНОЙ ВЫЧИСЛИ е относится к выч может быть исп с ик ользо:В Фиг ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР 1(56) Однородные вычислительныеАрхитектура и реализация: Докл.союзн. школы-семинара по параллобработке инаормации. Львов, 1901 репринт/ФМИ АН УССР; Р 41).Бусго 1 гс аггау сЬр щагсЪезрасе ог Ьд 8 Ь- Бреей ргосеззгпя.Е 1 есСгопдс Везг 8 п, 1984, .ОсгоЪе вано в составе специализированныхбыстродействуюндх вычислительных систем обработки изображений. Цель изобретения - увеличение быстродействия.Поставленная цель достигается тем,что процессор матричной вычислительной структуры содержит дешифратор 1,регистр 2 входа-выхода, регистр 3 первого операнда, регистр 4 второго операнда, триггер 5 переноса, блок 6 оперативнои памяти, первый и второй блоки 7 и 8 управления, распределитель9 импульсов, арифметико-логическийблок 10, триггер 11 переполнения,триггер 12 флага активности, триггер13 маски, триггер 14 загрузки, с первого по третий элементы 2 И-ИЛИ 15-17,элемент ИЛИ 18, коммутатор 19, магист"ральный элемент 20. 3 ил.19 1 ЬО входу регистра входа-выхода, к третьему информационному входу регистра первого операнда, к первому информационному входу регистра второго операнда и к инФормационному входу триггера загрузки, выход которого подключен к третьим входам режима первого и второго блоков управления, первый выход второго блока управления подключен к четвертому входу режима первого блока управления и к входу синхронизации блока оперативной памяти, второй выход второго блока управления подключен к входу чтения/записи блока оперативной памяти, четвертый и пятый информационные входы процессора подключены соответственно к первому и второму входам третьего элемента 2 И-ИЛИ, выход которого подключен к третьему информационному входу комму" татора и к второму информационному входу регистра второго операнда, первый выход которого подключен к третьему информационному входу регистра переполнения, второй выход регистра второго операнда подключен к четвертому информационному входу коммутатора и к четвертому информационному входу триггера переполнения, выходы с двенадцатого по двадцатый дешифратора подключены соответственно к первому и второму входам разрешения триггера загрузки, к второму и третьему входам первого элемента 2 И-ИЛИ, к управляющему входу магистрального элемента, к третьему и четвертому входам третьего элемента 2 И-ИЛИ, к третьему и к четвертому входам второго элемента 2 И-ИЛИ, тактовый вход процессора подключен к входу режима распределителя импульсов, первый и второй выходы которого подключены соответственно к первому и второму входам синхрониза 3395 20ции триггера загрузки, третий выходраспределителя импульсов подключен кпятому входу режима первого блока уп"равления и четвертому входу режима 5второго блока управления, третий выход регистра первого операнда подключен к первому информационному входуарифметико-логического блока, к третьему информационному входу регистравхода-выхода, к третьему информационному входу регистра второго операндаи к второму информационному входу блока оперативной памяти, третий информационный вход которого подключен кинформационному выходу арифметико-логического блока, выход переноса заемакоторого подключен к второму информационному входу триггера переноса, вы ход которого подключен к второму информационному входу триггера флагаактивности, к второму информационномувходу арифметико-логического блока, кпятому информационному входу триггера 25 переполнения и к четвертому информационному входу блока оперативной памяти, третий выход регистра второгооперанда подключен к третьему информационному входу арифметико-логического блока и к четвертому информационному входу регистра первого операнда,первый выход регистра входа-выходаподключен к пятому информационномувходу регистра первого операнда и кчетвертому информационному входу регистра второго операнда, второй выходрегистравхода-выхода подключен к. четвертому входу первого элемента2 И-ИЛИ, выход которого подключен к ,1 О информационному выходу процессора,вход-выход признака которого подключен к информационному входу-выходумагистрального элемента.1603395 Составитель В. СмирновРедактор Т. Пазоренко Техред М.Ходанич Корректор 0Ц Тираж 568 Подписноекомитета по изобретениям и открытиям при ГКНТ Москва, Ж, Раущская наб., д. 4/5 Производственно-издательский комбинат Заказ 3387ВНИИПИ Государственно11303 ент", г. Ужгород, ул. Гагарина, 101Изобретение относится к вычислительной технике и может быть использовано в составе специализированныхбыстродействующих вычислительных сис 5тем обработки изображений,Цель изобретения - повышение быстродействия.На Фиг. 1 представлена схема процессора; на Фиг. 2 - схема первогоблока управления; на фиг, 3 - схемавторого блока управления.Процессор содержит дешифратор 1,регистр 2 входа-выхода, регистр 3 первого операнда,. регистр 4 второго операнда, триггер 5 переноса, блок 6 оперативной памяти, первый 7 и второй 8блоки, управления, распределитель 9импульсов, арифметико-логический блок10, триггер 11 переполнения, триггер щ12 Флага активности, триггер 13 маски,триггер 14 загрузки, первый элемент2 И-ИЛИ 15, второи элемент 2 И-ИЛИ 16,третий элемент 2 И-ИЛИ 17, элементИЛИ 18, коммутатор 19, магистральный 25элемент 20, вход-выход 21 признака,информационный выход 22, выхо;, 23 пер.вого операнда, выход 24 второго операнда, адресный вход 25, вход 26 кодаоперации, первый информационный вход27, тактовый вход 28, со второго попятый информационные входы 29-32 процессора. Первый блок управления содержит с первого по двадцать третий элементы И 33-55 с первого по двенадца35тый элементы ИЛИ 56-67, с первого потретий элементы 2 И-ИЛИ 68-70, второйблок управления содержит триггер 71,с первого по третий элементы ИЛИ 7274, элемент И 75 и элемент 2 И-ИЛИ 76.Устройство работает следующим образом.Микрокоманда, поступающая на дешифратор 1 через входы 26, разбита напять полей и обеспечивает параллельное выполнение пяти операций в процес.соре.Первое поле управляет работой регистра 2 входа-выхода, второе и третье - работой регистров 3 и 4 и триг 50геров переполнения 11, Флага активности 12 и маски 13, четвертое - работойтриггеров переноса 5 и,загрузки 14,пятое - работой блока 6 оперативнойпамяти. Загрузка процессора информацией выполняется одновременно с обработкой информации.Триггеры флага активности 12 и маски 13 гозволяют блокировать выполнение операцией в процессоре. Блокировка выполнения микрокоманд происходитединичными сигналами с выходов триггеров Флага активности 12 и маски 13,которые, поступая на входы элементаИЛИ 18, формируют на его выходе сигнал блокировки. Этот сигнал запрещаетформирование сигналов, позволяющих выполнить в процессоре соответствующуюмикрокоманду,Выполнение одной микрокоманды осуществляется за два периода импульсовтактовой частоты, поступающих на вход28 тактовой частоты. Распределитель9 импульсов из последовательности импульсов тактовой частоты Формируетпоследовательность сигналов : ТИ 1на время длительности первого полупериода, ТИ 2 - на время длительности втовторого полупериода, ТИЗ - на времядлительности третьего полупериода, которые синхронизируют работу процессора, поступая на блоки 7 и 8 управленияи триггер 14 загрузки.Триггер 14 загрузки позволяет про-.изводить загрузку информации, поступающей через вход 27 в процессор, непрекращая ее обработку, Установкатриггера 14 загрузки в режим загрузкиосуществляется по сигналу, приходящему с соответствующего выхода деШифратора 1 на вход триггера 14 загрузки,который формируется дешифратором 1при расшиФровке им микрокоманды приемаинформации с входа 27 в регистр 2 входа-выхода, простробированному импульсом ТИ 1, который поступает с соответствующего выхода распределителя 9 импульсов или по сигналу, который формируется дешифратором 1 при расшиФровкеим микрокоманды записи информации(единицы) из блока 6 памяти в триггер14 загрузки, простробированному импульсом ТИЗ. Так как прием информации осуществляется обычно с экрана по строкам, то и в матрицу процессоров системы ин" формация загружается по строкам или по столбцам. Таким образом, устанавливая в "1" триггеры загрузки необходимой строки (столбца), осуществляется запись информации в процессоры системы, т.е. происходит загрузка матрицы. Наличие триггера 14 загрузки позволяет существенно сократить объем буфера для промежуточного хранения информа-. ции, поступающей с экрана, так как в16030этом случае необходим буфер не навесь экран, а только на одну строку,Сброс режима загрузки осуществляется по микрокоманде записи информации из блока 6 в триггер 14 загрузкив случае, если в триггер 14 записывается ноль.Регистр 2 входа-выхода служит дляпреобразования последовательной информации, поступающей через вход 27,в параллельную и передачи ее на выход22. Регистр 2 входа-выхода осуществляет прием входной информации, прием инФормации с регистра 3 первого операнда, прием информации из блока 6.Прием последовательной информации,поступающей через вход 27 в регистр 2входа-выхода, осуществляется по соответствующей микрокоманде. По этой 20микрокоманде дешифрато р 1 вырабатывает сигнал, устанавливающий триггер14 загрузки в режим загрузки. Единичный сигнал с выхода триггера 14 загрузки поступает на второй вход элемента И 06 и на первый вход элементаИ 42. На первый вход элемента И 06поступает сигнал ТИ 1, а на второйвход элемента И 42 - сигнал ТИ 2, который вырабатывается распределителем9 импульсов. С выхода элемента И 42сигнал поступает на один из входовэлемента ИЛИ 56, В результате этогона выходах элементов И 06 и ИЛИ 56формируются импульсы, которые поступают на регистр 2 входа-выхода и осуществляют запись в него информации,приходящей с входа 27.Во время выполнения микрокомандыприема входной информации в регистр2 входа-выхода осуществляется выдачаинформации, содержащейся в младшемразряде этого регистра, с его выходана третий вход элемента 2 И-ИЛИ 15.На первый вход элемента 2 И-ИЛИ 15 пос 45тупает единичный сигнал с соответствующего выхода дешифратора 1, которыйпоказывает, что выполняется микрокоманда приема входной информации, иразрешает прохождение содержимогомладшего разряда регистра 2 входа-выхода через элемент 2 И-ИЛИ 15 на выход22 процессора,В процессоре предусмотрена микрокоманда, которая позволяет осуществлять передачу информации, посту 55пающей через вход 27 на выход 22, минуя регистр 2 входа-выхода. Во времяее выполнения информация с входа 27 95 6поступает на второй вход элемента 2 И-ИЛИ 15, а на четвертый его вход поступает единичный сигнал соответствующего выхода дешифратора 1 и разрешает прохождение информации с выхода элемента 2 И-ББ 1 15 на выход 22 процессора.Выполнение микрокоманд обнуления содержимого регистра 2 входа-выхода осуществляется только в режиме загрузки. С выхода триггера 14 загрузки единичный сигнал проходит на третий вход элемента И 04. На два других входа этого элемента поступают сигнал с дешифратора 1, показывающий, что выполняется микрокоманда обнуления регистра 2 входа-выхода и сигнал ТИ 1 с распределителя 9 импульсов. На выходе элемента И 04 Формируется сигнал, который, поступая на регистр 2 входа-выхо" да, осуществляет его обнуление,Запись информации, содержащейся в регистре 3 первого операнда или в блоке 6, в регистр 2 входа-выхода происходит при выполнении процессором соответствующих микрокоманд. Дешифратор 1 расшифровывает код одной из этих микрокоманд и вырабатывает единичный сигнал, поступающий на второй вход второго элемента И элемента 2 И-ИЛИ 68 элемента при осуществлении переписи информации в регистр 2 входа-выхода из регистра 3 первого операнда, или единичный сигнал, поступающий на второй вход первого элемента И элемента 2 И-ИЛИ 68 при осуществлении записи информации в регистр 2 входа-выхода из блока 6. На первые входы первого и второго .элементов И элемента 2 И-ИЛИ 68 поступают стробирующие импульсы ТИЗ и ТИ 2 соответственно, вырабатываемые распределителем 9 импульсов, а на третий вход первого элемента И элемента 2 И-ИЛИ 68 поступает единичный сигнал выборки с выхода элемента 2 И-ИЛИ 76. Сформировавшиеся единичные сигналы с выхода элемента 2 И-И 31 И 68 поступают на вход элемента И 00. Если на его инверсном входе находится нулевой уровень (выполнение этих микрокоманд не замаскировано), то с выхода элемента И 00 единичный сигнал поступает на второй вход элемента ИЛИ 56, а с его выхода - регистр 2 входа-выхода, осуществляя запись с него информации.Регистр 0 первого операнда служит для преобразования последовательной информации, поступающей через входы29, 30 или через вход-выход 21, в параллельную и передачи ее на выход 23первого операнда или на вход-выход 21,По соответствующим микрокомандам врегистре 3 первого операнда можетбыть выполнен сдвиг его содержимоговправо (в сторону младших разрядов)или влево (в сторону старших разрядов)с занесением содержимого выдвигаемого 10разряда в триггер 11 переполнения, атакже может быть записана единица вмладший разряд регистра 3 первого операнда,Прием информации в регистр 3 первого операнда свходов 29 и 30 и входа-выхода 21 осуществляется по микрокомандам.Информация с входов 29 и 30 поступает на второй и третий входы элемента 2 И-ИЛИ 16. На первый и четвертыйвходы этого элемента поступают единичные сигналы с соответствующих выходов дешифратора 1, которые показывают,что выполняется одна из микрокоманд 5.приема информации в регистр 3 первогооперанда с входов 29 и 30 и разрешаютпрохождение информации с одного изэтих входов через элемент 2 И-ИЛИ 16на вход регистра 3 первого операнда. 30При выполнении микрокоманды записиинформации, поступающей через входвыход 21 на магистральный элемент 20,в регистр 3 первого операнда дешифратор 1 вырабатывает единичный сигнал,который разрешает прохождение информации с его выхода на вход регистра 3первого операнда.Запись информации в регистр 3 первого операнда выполняется в два этапа.40Сначала по импульсу ТИ 1 с распределителя 9 импульсов, информация записывается во вспомогательный регистр, азатем по импульсу ТИ 2 с распределителя 9 импульсов - в основной. Единичный сигнал с. дешифратора 1, определяющий, что выполняется одна из этикмикрокоманд, поступает на первый, второй или четвертый вход элементаИЛИ 61, формируя при наличии импульсаТИ 1 и отсутствии маскирования черезэлемент И 37 сигнал записи во вспомо-.гательный регистр, а при наличии сигнала ТИ 2 и отсутствии маскирования через элементы ИЛИ 60, 2 И-ИЛИ 70 иИ 43 сигнал записи информации в основнойрегистр 3 первого операнда,При выполнении операций сдвига изаписи единицы в младший разряд регистра 3 первого операнда дешифратор1 вырабатывает единичные сигналы, которые поступают на третий, пятый ишестой входы элемента ИЛИ 61 в зависимости от кода выполняемой микрокоманды. С его выхода единичный сигналприходит на третий вход элементаИЛИ 60 и на второй вход элемента И 37,Далее сигналы, позволяющие выполнитьодну из этих микрокоманд, формируются аналогично рассмотренным выше.Микрокоманды записи в регистр 3 перпервого операнда информации из блока6, из регистров 2 - и 4 выполняютсяследующим образом. Дешифратор 1 выра- .батывает единичные сигналы, которыепоступают на второй вход первого элемента И элемента 2 И-ИЛИ 70 при выполнении операции записи информации изблока 6 или .на первый или второй входы элемента ИЛИ 60 при выполнении операций записи информации из регистров2 или 4 соответственно в регистр 3первого операнда.Регистр 4 второго операнда служитдля преобразования последовательнойинформации, поступающей через входы32 или 31, в параллельную и передачиее на вход 24 второго операнда, Ре"гистр 4 второго операнда осуществляетприем информации, поступающей черезвходы 32 или 31, прием информации срегистров 2 и 3 и прием информациииз блока 6.По соответствующим микрокомандамв регистре 4 второго операнда можетбыть выполнен сдвиг его содержимоговправо (в сторону младших разрядов)или влево (в сторону старших разрядов)с занесением (без занесения) содержимого выдвигаемого разряда в триггер11 переполнения, а также может бытьзаписана единица в младший разряд регистра 4 второго операнда,Информация с входов 32 и 3 1 поступает на второй и третий входы элемента 2 И-ИЛИ 17. На первый и четвер-.тый входы этого элемента поступаютединичные сигналы с соответствующихвыходов дешифратора 1, которые показывают, что выполняется одна из микрокоманд приема информации в регистр 4второго операнда с входов 32, 31, иразрешают прохождение информации с одного из этих входов на вход регистра4 второго операнда.Единичный сигнал с дешифратора 1поступает на первый или второй входыэлемента ИЛИ 63, йормируя сигнал записи во вспомогательный регистр, а при наличии ТИ 2 и отсутствии маскирования - сигнал записи информации в основной регистр,При выполнении операций сдвига и записи единицы в мпадший разряд регистра 4 первого операнда дешифратор 1 вырабатывает сигналы, которые поступают на третий, четвертый, пятый и шестой входы элемента ИЛИ 63 в зависимости от кода выполняемой микрокоманды. С его выхода единичный сигнал приходит на первые входы элементов И 45 и ИЛИ 62. Далее сигналы, позволяющие выполнить одну из этих микроко" манд, формируются аналогично рассмотЪренным выше.Микрокоманды записи в регистр 4 второго операнда инФормации из блока 6, из регистров входа-выхода 2 и первого операнда 3 выполняются следующим образом. Дешийратор 1 вырабатывает единичные сигналы, которые поступают на второй вход первого элемента И элемента 2 И-ИЛИ 69 при выполнении операции записи информации из блока 6 или на второй или третий входы элемента ИЛИ 62 при выполнении операций записи информации из регистров входа- выхода 2 или первого операнда 3, формирующие сигнал записи в основной регистр информации.При выполнении процессором микро- команд приема информации в регистр 3 первого операнда с входов 29 или 30 происходит выдача инйормации, содержащейся в младшем разряде регистра 3 первого операнда, на вход коммутатора 19,а затем на выход 23 первого операнда в случае, если выполнение этих микрокоманд не маскируется единичным сигналом с выхода элемента ИЛИ 18.Единичный сигнал с выхода элемента И 52 поступает на коммутатор 19 и разрешает выдачу инйормации из младше" го разряда регистра 3 первого операнда через коммутатор 19 на выход 23 первого операнда.Если на инверсный вход элемента И 52 поступает единичный сигнал с выхода элемента ИЛИ 18, то выполнение микрокоманд записи информации в регистр 3 первого операнда с входа 29 или 30 блокируется. В этом случае этот единичный сигнал поступает на первый вход элемента И 54, на второйего вход поступает единичный сигнал 10 15 20 25 30 35 40 45 50 55 с выхода элемента ИЛИ 66. В результате на выходе элемента И 54 формируется единичный сигнал, который разрешает прохождение инйормации на выход 23 первого операнда с входа 29 или 30 в зависимости от кода поступающей микрокоманды.Таким образом, если выполнение микрокоманд записи инйормации в регистр 3 первого операнда маскируется в процессоре, то информация с этих входов в зависимости от кода выполняемой микрокоманды поступает на выход 23 первого операнда без занесения ее в регистр 3 первого операнда.При выполнении процессором микро- команд приема инйормации в регистр 4 второго операнда с входов 32 или 31 происходит выдача информации, содержащейся в младшем разряде регистра 4 второго операнда на инйормационный вход коммутатора 19, а затем на выход 24 второго операнда в случае, если выполнение этих микрокоманд. не маскируется единичным сигналом с выхода элемента ИЛИ 18.Единичный сигнал с выхода элемейта И 53 поступает на коммутатор 19 и разрешает выдачу инйормации из младшего разряда регистра 4 второго операнда через коммутатор 19 на выход 24 второго операнда,Если на инверсный вход элемента И 53 поступает единичный сигнал с выхода элемента ИЛИ 18, то выполнение микрокоманд записи информации в регистр 4 второго операнда с входов 32 или 31 блокируется. В этом случае единичный сигнал поступает на первый вход элемента И 55, на второй его вход поступает единичный сигнал с выхода элемента ИЛИ 67. В результате на выходе элемента И 55 йормируется единичный сигнал, который поступает на коммутатор 19, разрешая прохождение информации на выход 24 второго операнда с входов 32 или 31 (в зависимости от кода поступающей микрокоманды).Таким образом, если выполнение микрокоманд записи инйормации в регистр 4 второго операща маскируется в процессоре, то информация с этих входов в зависимости от кода выполняемой микро- команды поступает на выход 24 второго операнда без занесения ее в регистр 4 второго операнда.Обнуление регистров 3 и 4 выполняется по микрокомандам. Дешифратор 111 160339 при расшифровке кодов. этих микроко"- манд вырабатывает единичные сигналы, которые поступают на вторые входы элементов И 38 при обнулении регистров 3 первого операнда и И 39 при обнулении5 регистра 4 второго операнда. На первые входы этих элементов поступают импульсы ТИ 1, вырабатываемые распределите-,. лем 9 импульсов. Если на инверсные входы элементов И 38 и 39 поступает нулевой сигнал с выхода элемента ИЛИ 18, то на выходах элементов И 38 и 39 формируются единичные сигналы, которые поступают на регистры 3 и 4 и производят обнуление этих регистров.Арифметико-логический блок 10 выполняет следующие операции над 4-разрядными операндами: логическое сложение, логическое умножение, сложение, 20 вычитание, суммирование по шой 2, инверсия. Выполнение этих операций над 4-разрядными операндами, поступающими на арифметико-логический блок 1 О, осуществляется в нем постоянно, а резуль тат выполнения одной из этих операций записывается в блок 6 только при наличии соответствующей микрокоманды.Блок 6 оперативной памяти предназначен для хранения информации, посту С пающей с регистров 2 и 3 и с арифмети" ко-логического блока 10, а также содержимого триггеров 5 и 14. Передача информации из блока 6 может происходить во все регистры процессора и триггеры 13 и 14 по соответствующим35 микрокомандам.В процессоре выполняются семь микрокоманд записи информации в блок 6 оперативной памяти: результат логического сложения, результат суммирования по шой 2, результат логического умножения, результат суммы (разности) и пять микрокоманд чтения инФормации из блока 6: в регистр 2 входа-выхода, в регистр 3 первого операнда, в регистр 4 второго операнда, в триггер 13 маски и триггер 14 загрузки.При выполнении одной из микро- команд записи информации в блок 6 дешифратор 1 в зависимости от кода микрокоманды вырабатывает единичный сигнал, который поступает на один из восьми входов элемента ИЛИ 74 С его выхода этот сигнал поступает на инверсный вход элемента ИЛИ 2, а с его выхода. нулевым сигналом на соответст,вующий вход блока 6. 12При выполнении одной из микрокоманд чтения информации из блока 6 дешифратор 1 в зависимости от кода микрокоманды вырабатывает сигнал, который поступает на один из пяти входовэлемента ИЛИ 73. С его выхода этотсигнал поступает на вход элементаИЛИ 72, а с его выхода единичным сигналом - на соответствующий входблока 6.Элемент 2 И-ИЛИ 76 Формирует сигналвыборки, который разрешает обращениек блоку 6 при выполнении микрокомайдзаписи или чтения информации в (из)блок 6. На первые входы первого ивторого элементов И элемента 2 И-ИЛИ 72поступают единичные сигналы с выходовэлементов ИЛИ 73 и 74 соответственно,определяющие, что выполняется одна измикрокоманд чтения .или записи информации из (в) блока 6. На вторые входыпервого и второго элементов И элемента 2 И-ИЛИ 76 поступает единичный сигнал с триггера 71, длительность которого определяется интервалом между передними Фронтами импульсов ТИ 2 и ТИ 1,вырабатываемыми распределителем 9 импульсов и поступающими на 8- иК-входы триггера соответственно. Наинверсный вход первого элемента и элеэлемента 2 И"ИЛИ 76 поступает сигнал свыхода элемента ИЛИ 18. Если он нуле-.вой, Формируется единичный сигнал выборки, поступающий на соответствующийвход блока 6, и, следовательно, выполняется операция чтения информациииз блока 6. Если на выходе элементаИЛИ 18 сформировался единичный сигнай,то он, приходя на инверсный вход первого элемента И элемента 2 И-ИЛИ 76,запрещает Формирование сигнала выборки и чтение информации из блока 6 непроисходит,Сигнал с выхода элемента ИЛИ 18приходит также на первый вход элемента И 75, на инверсный его вход приходит сигнал с выхода триггера 14 загрузки. Если на выходе триггера 14загрузки сформировался нулевой уровень (нет режима-загрузки), то единичный сигнал с выхода элемента ИЛИ 18проходит на выход элемента И 75 и наинверсный вход второго элемента И элемента 2 И-ИЛИ 76, запретив тем самымформирование сигнала выборки на выхо"де элемента 2 И-ИЛИ 76 и, следовательно, выполнение операций записи информации в блок 6. Если на выхаы зле13 14 ничный сигнал, осуществляющий егоустановку в "О",Триггер 11 переполнения служит длязаписи и хранения значения вьдвигаемых разрядов из регистров 3 и 4 привыполнении в них операций сдвига сзанесением вьдвигаемой информации втриггер 11 переполнения.Единичный сигнал, вырабатываемыйдешифратором 1 при расшийровке кодаодной из микрокоманд сдвига с занесением вьдвигаемой информации в триггер 11 переполнения, поступает наодин из четырех входов элемента ИЛИ 59.С его выхода единичный сигнал приходит на первый вход элемента И 49, навторой вход которого поступает сигналТИ 1, формируемый распределителем 9импульсов. Если на инверсный входэлемента И 48 приходит нулевой сигнал с выхода элемента ИЛИ 18, разрешающий выполнение микрокоманды обнуления триггера 5 переноса, то на выходеэлемента И 48 йормируется единичныйсигнал, осуществляющий его установкув нОТриггер 11 переполнения служит длязаписи и хранения значения выдвигаемых разрядов из регистров 3 и 4 привыполнении в них операций сдвига с занесением вьдвигаемой информации втриггер 11 переполнения.Единичный сигнал, вырабатываемыйдешифратором 1 при расшийровке кодаодной из микрокоманд сдвига с занесением вьдвигаемой информации в триггер11 переполнения, поступает на один изчетырех входов элемента ИЛИ 59. С еговыхода единичный сигнал приходит напервый вход элемента И 49, на второйвход которого поступает сигнал ТИ 1,формируемый распределителем 9 импульсов. Если на инверсный вход элемента И 49 приходит нулевой сигнал свыхода элемента ИЛИ 18, разрешающийвыполнение микрокоманды сдвига, тона выходе элемента И 49 формируетсяединичный сигнал, который поступаетна триггер переполнения и осуществляет запись в него информации, выдвигаемой из регистра 3 или 4 в зависимости от выполняемой микрокоманды.Выдвигаемая из регистров 3 и 4информация поступает на соответствующие входы триггера 11 переполнения.Сигналы, определяющие какая именно информация должна быть записана в триггер 11 переполнения, формируются ле 1603395мента ИЛИ 18 сформировался нулевойсигнал, то осуществляется запись информации в блок 6.В режиме загрузки на инверсный входэлемента И 75 с выхода триггера 145загрузки поступает единичный уровень,который йормирует на выходе элементаИ 75 нулевой сигнал . Этот сигнал, поступая с выхода элемента И 75 на инверсный вход второго элемента И элемента 2 И-ИЛИ 76, разрешает йормирование сигнала выборки на выходе элемента 2 И-ИЛИ 76 и, следовательно, выполнение операции записи инйормации вблок 6.Триггер 5 переноса служит для хранения значення переноса (заема), которое возникает при выполнении арифметико-логическим блоком 10 операций 20сложения (вычитания) над 4-разрядными операндами.Занесение значения переноса или заема в триггер 5 переноса и записи внего единицы может быть выполнено по 25соответствующим микрокомандам. Единичный сигнал, вырабатываемый дешифратором 1 поступает на один из трехвходов элемента ИЛИ 65, С выхода элемента ИЛИ 65 единичный сигнал поступает на второй вход элемента И 47,на первый вход которого поступает сигнал ТИ 1, вырабатываемый распределителем 9 импульсов. Если микрокомандане маскируется, то на выходе элементаИ 47 формируется единичный сигнал, ко 35торый поступает на триггер 5 переносаи осуществляет запись в него соответствующей информации (переноса, заемаили единицы). Сигналы, определяющиекакая именно инйормация должна бытьзаписана в триггер 5, вырабатываютсядешифратором 1 при расшифровке кодавыполняемой микрокоманды, разрешаяпрохождение информации на вход триггера 5 переноса,Обнуление триггера 5 переноса осу-;ществляется по микрокомацце. Дешифратор 1 при выполнении этой микрокомандывырабатывает единичный сигнал, который 5 Опоступает на второй вход элементаИ 48, а на второй вход этого элемента приходит сигнал ТИ 1, йормируемый распределителем 9 импульсов. Если на инверсный вход элемента И 48 приходит нулевой сигнал с выхода элемента ИЛИ 18,разрешающий выполнение микрокомандыобнуления триггера 5 переноса,. то навыходе элемента И 48 формируется еди39516Запись информации в триггер 12 фла.га активности с входа 27 или иэ триггера 5 переноса осуществляется присоответствующей микрокоманде. Единичный .сигнал, вырабатываемый дешифратором 1, поступает на один из входовэлеменТа ИЛИ 64, с выхода которого онприходит на второй вход элемента И 46,на первый вход этого элемента поступает импульс ТИ 1, Формируемый распределителем 9 импульсов. Если на инверсный вход элемента И 46 поступает нулевой сигнал с выхода элемента ИЛИ 18,разрешающий выполнение этих микроко)5манд, то на выходе элемента И 46вырабатывается единичный сигнал, разрешающий выполнение микрокоманды запи"си информации в триггер 12 Флага ак 20 тивности с входа 2/ или из триггера 5переноса,Выполнение микрокоманды записи информации в триггер 13 маски из блока6 происходит следующим образом. Дешифратор 1 вырабатывает единичный. сигнал, поступающий на первый входэлемента И 40, на второй вход которого поступает импульс ТИЗ, Формируемыйраспределителем 9 импульсов, а натретий его вход поступает единичныйсигнал выборки, который формируетсяна выходе элемента 2 И-ИБ 1 76. В результате на выходе элемента И 40 Формируется единичный сигнал, которыйпоступает на первый вход элемента57 а с его выхода - на вход триггера 13 маски, осуществляя запись инФормации в него из блока 6.Запись содержимого триггера 11 переполнения в триггер 13 маски проис 15 1603 шифратором 1 и определяются кодом выполняемой микрокоманды.По соответствующей микрокоманде выполняется перезапись информации, содержащейся в триггере 5 переноса в триггер 11 переполнения, При выполнении этой микрокоманды дешифратор 1 Формирует единичный сигнал, который поступает на первый вход элемента И 50, на второй его вход приходит сигнал ТИЗ, Формируемый распределителем 9 импульсов. Если на инверсный вход элемента И 50 приходит нулевой сигнал с выхода элемента ИЛИ 18, разрешающий выполнение микрокоманды, то на выходе элемента И 50 Формируется единичный сигнал, который осуществляет запись триггера 11 переполнения информации с выхо да триггера 5 переноса.Если на выходе одного из триггеров 12 и 13 будет единичный сигнал, то этот сигнал блокирует выполнение микрокоманд.Обработка информации в матрице, построенной на основе процессоров происходит параллельно. При реализации конкретных алгоритмов не все процессоры должны выполнять поступающие на них микрокоманды. Для реализации используется триггер 13 маски. Если он установлен в единичное состояние, то выполнение микрокоманд процессором блокируется.При использовании матрицы процессоров в качестве ассоциативной памяти необходим триггер 12 Флага активности, который позволяет по какому-то ключу ипи признаку устанавливать процессоры в активное или пассивное состояние.По соответствующим микрокомандам 4 О в триггер 12 Флага активности записывается либо содержимое триггера 5 переноса, либо единица, либо информация, поступающая через вход 27.При выполнении в процессоре микро- ф 5 команды записи единицы в триггер 12 флага активности дешифратор 1 вырабатывает единичный сигнал, поступающий на второй вход элемента И 51, На первый вход этого элемента поступает 50 импульс ТИ 1, Формируемый распределителем 9 импульсов. Если на инверсном входе элемента И 51 находится нулевой сигнал, то на выходе элемента И 51 Формируется единичный сигнал, 55 который приходит на соответствующий вход триггера 12 Флага активности и осуществляет запись единицы в триггер 12 Флага активности. ходит по микрокоманде, во время которой дешифратор 1 вырабатывает единичный сигнал, который поступает на первый вход элемента И 41, на второйвход этого элемента поступает сигналТИ 2, Формируемый распределителем 9 импульсов. С выхода элемента И 41единичный сигнал приходит на третийвход элемента ИЛИ 57, с выхода которого он поступает на вход триггера 13маски, осуществляя запись в него информации из триггера 11 переполнения.При выполнении в процессоре микро- команд записи в триггер 13 маски дешифратор 1 вырабатывает единичные сигналы, поступающие на один из трех входов элементов ИЛИ 58 в зависимости от выполняемой микрокоманды. С выхода элемента ИЛИ 58 единичный сигнал приходит на второй вход элемента И 35,1 б 0339 на первый вход которого поступает им" пульс ТИ 1, вырабатываемый распределителем 9 импульсов. С выхода элемента И 35 единичный импульс поступает на второй вход элемента ИЛИ 57, с выхода которого он поступает на вход триггера 13 маски, осуществляя в нем выполнение рассматриваемых микрокоманд.Выдача информации на вход-выход 21 происходит с первого выхода регистра 3 первого операнда по соответствующей микрокоманде. Информация с первого выхода регистра 3 первого операнда поступает на информационный вход ма гистрального элемента 20. На его управляющий вход поступает единичный сигнал, который разрешает прохождение информации с выхода регистра 3 первого операнда на вход-выход 21, 20 формула из обр ет ения Процессор матричной вычислительной системы, содержащий регистр входа-выхода, регистр первого операнда, регистр второго операнда, блок оперативной памяти, триггер переноса и дешифратор, причем вход кода операции процессора подключен к входу дешифратора, вход режима процессора подключен к адресному входу блока памяти, первый информационный вход процессора подключен к первому информационному входу регистра входа-выхода, первый, второй и третий выходы дешифратора подключены соответственно к входам синхронизации регистра входа-, выхода, регистра первого операнда и регистра второго операнда, о т л ич а ю щ и й с я тем, что, с целью повышения быстродействия, он содержит распределитель импульсов, с первого по третий элементы 2 И-ИЛИ, первый и второй блоки управления, триггер загрузки, триггер переполнения, триггер переноса, триггер флага активности, триггер маски, элемент ИЛИ, магист.ральный элемент, коммутатор и арифметико-логическии блок, причем первый информационный вход процессора подключен к первому входу первого элемента 2 И-ИЛИ, к первому информационному входу триггера Флага и к первому.информационному входу триггера маски, прямой выход которого подключен к пер-вому входу элемента ИЛИ, выход кото-. рого подключен к первым входам режима первого и второго блоков управления,5 18с первого по четырнадцатый выходы первого блока управления подключены соответственно к первому информационному входу триггера переноса, к входузаписи у считывания и к входу установки в "О" регистра входа-выхода, к вхо"ду установки в " 1" триггера Флагй активности, к входу записи , считыванияи к входу установки в "О" регистрапервого операнда, к входу записи-считывания и к входу установки в "О" регистра второго операнда, к входу синхронизации и входу установки в "О"триггера переполнения, к входу синхронизации и к входу установки в "О"триггера маски, к входу записи триггера влага активности и к управляющемувходу коммутатора, первый и второйвыходы которого подключены соответственно к выходам первого и второго операндов процессора, с четвертого поодиннадцатый выходы дешифратора подключены соответственно к второму входу режима первого блока управления, квторому входу режима второго блокауправления, к входу кода операцииарифметико-логического блока, к входу разрешения триггера переполнения,к входу разрешения триггера маски,к входу синхронизации и к входу установки в "О" триггера переноса и к вхо.ду синхронизации. триггера Флага активности, выход которого подключен квторомувходу элемента ИЛИ, второй итретий информационные входы процессора подключены соответственно к первому и второму входам второго элемента2 И-ИЛИ, выход которого подключен кпервому информационному входу коммутатора и первому информационному входу регистра первого операнда, первыйвыход которого подключен к первомуинформационному входу триггера переполнения, к второму информационномувходу коммутатора и к информационному1входу магистрального элемента, выходкоторого подключен к второму информационному входу регистра первогооперанда, второй вход которого подключен к второму информационному входу триггера переполнения, выход которого подключен к второму информационному входу триггера маски и к первомуинформационному входу блока оперативной памяти, выходы с первого по пятыйкоторого подключены соответственно ктретьему информационному входу триггера маски к второму информационному

СмотретьЗаявка

4343719, 12.10.1987

ПРЕДПРИЯТИЕ ПЯ Р-6052

САДОВНИКОВА АНТОНИНА ИНОКЕНТЬЕВНА, ХРУСТАЛЕВ АЛЕКСЕЙ НИКОЛАЕВИЧ, БУТУЗОВ ВЛАДИМИР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 15/173, G06F 7/00

Метки: вычислительной, матричной, процессор, системы

Опубликовано: 30.10.1990

Код ссылки

<a href="https://patents.su/12-1603395-processor-matrichnojj-vychislitelnojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Процессор матричной вычислительной системы</a>

Предыдущий патент: Устройство сопряжения

Следующий патент: Устройство для определения параметров графа

Случайный патент: Способ переработки низкокачественных диаспоровых бокситов