Устройство для вычисления степенных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1282120

Автор: Глазачев

Текст

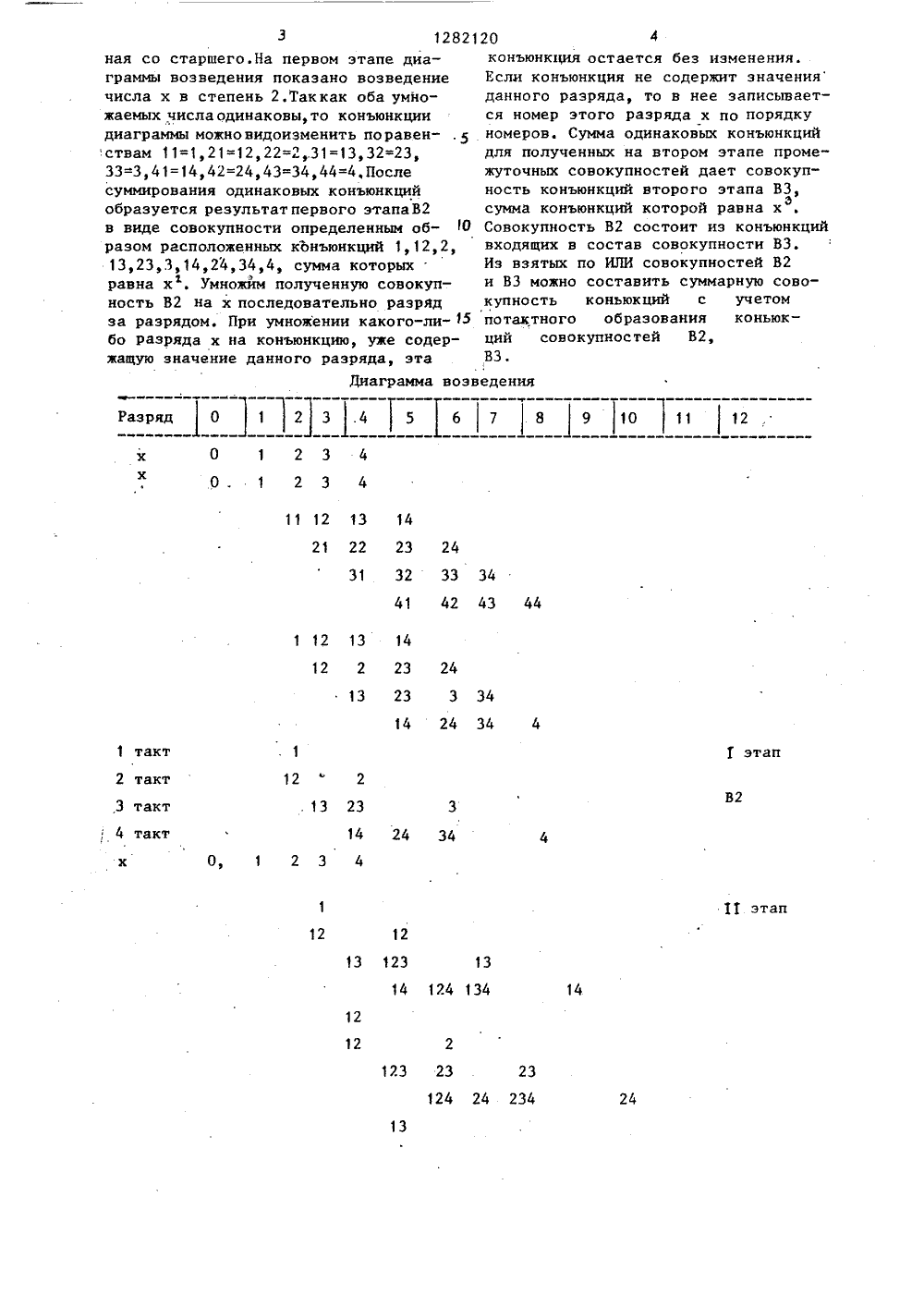

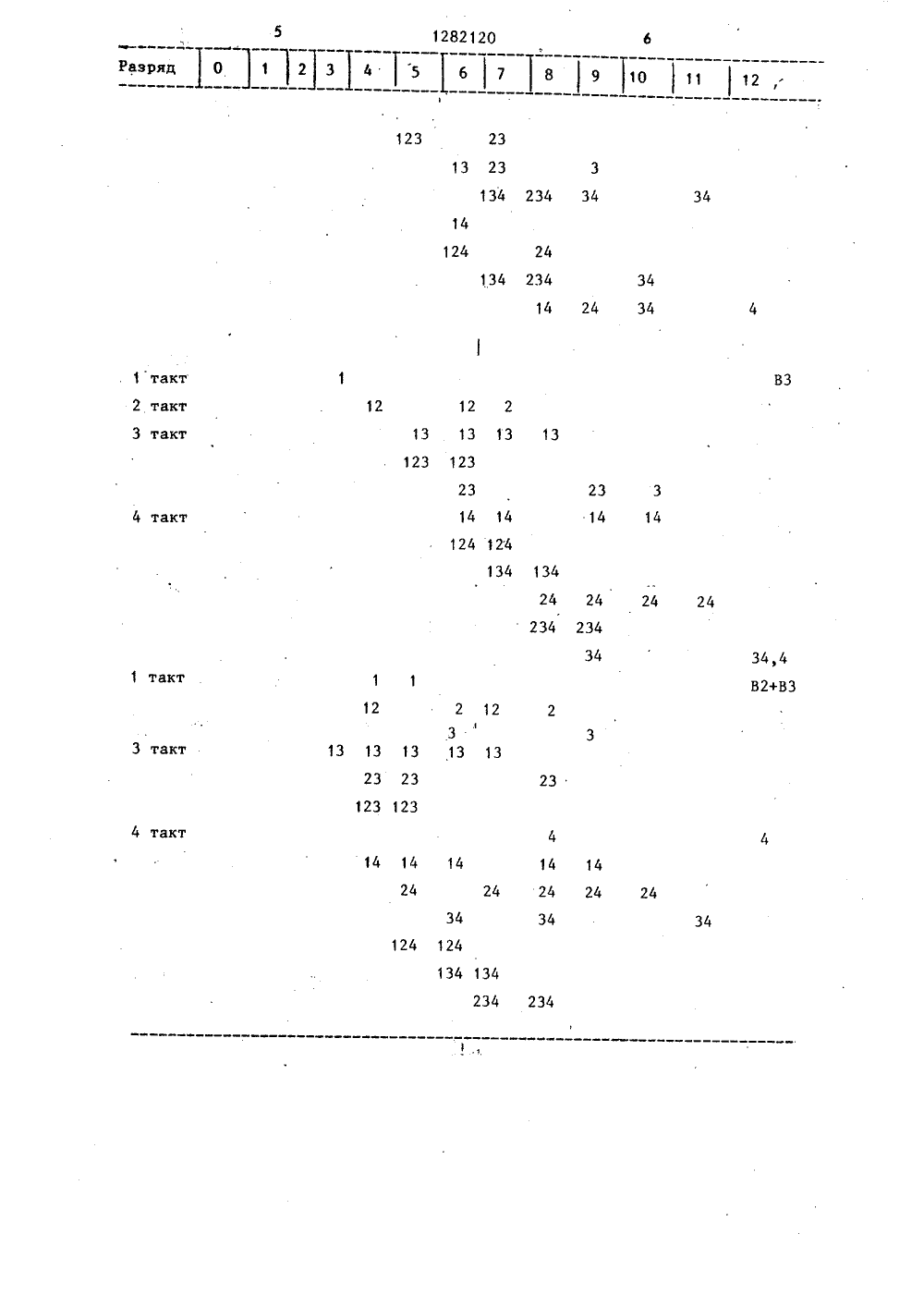

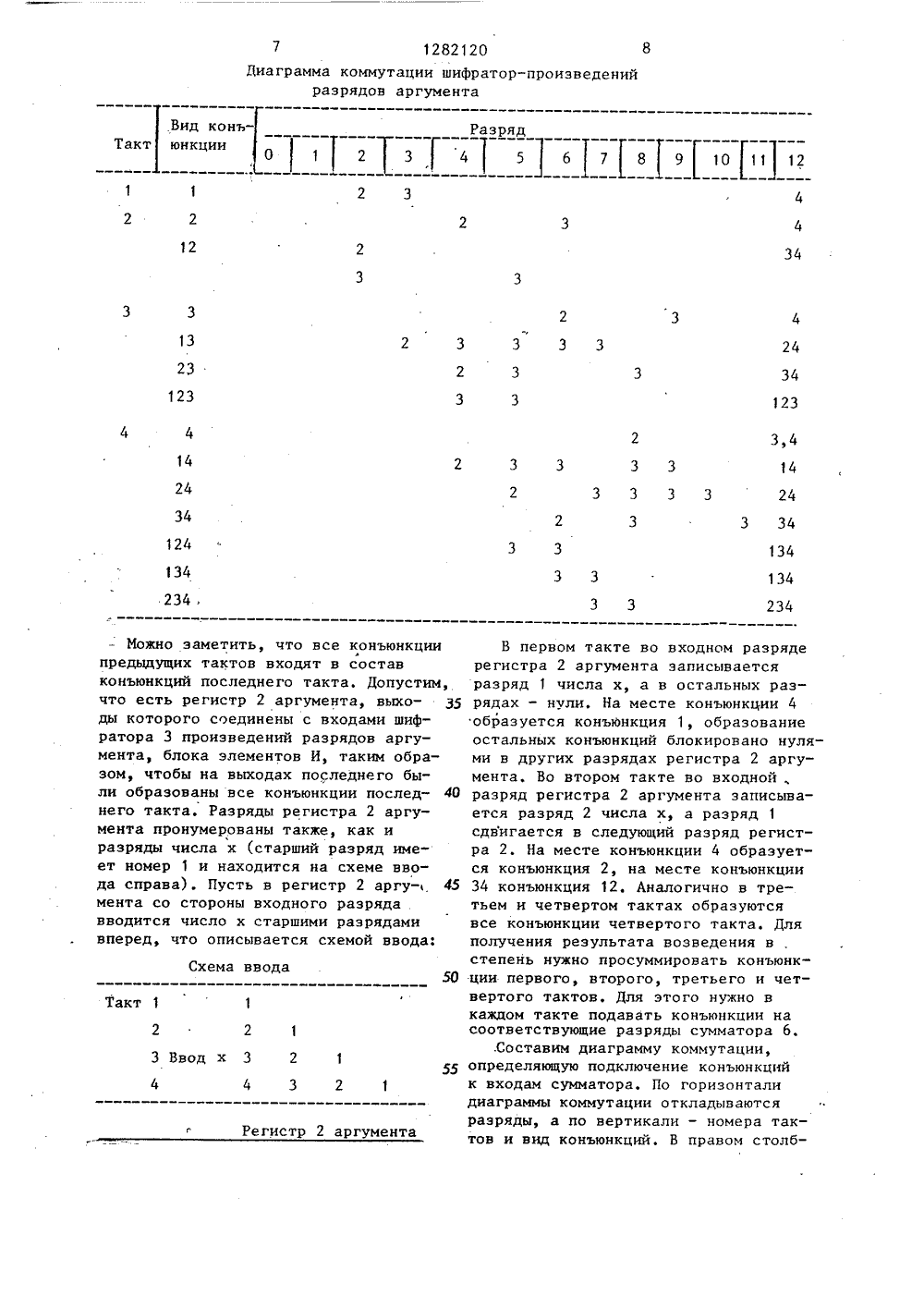

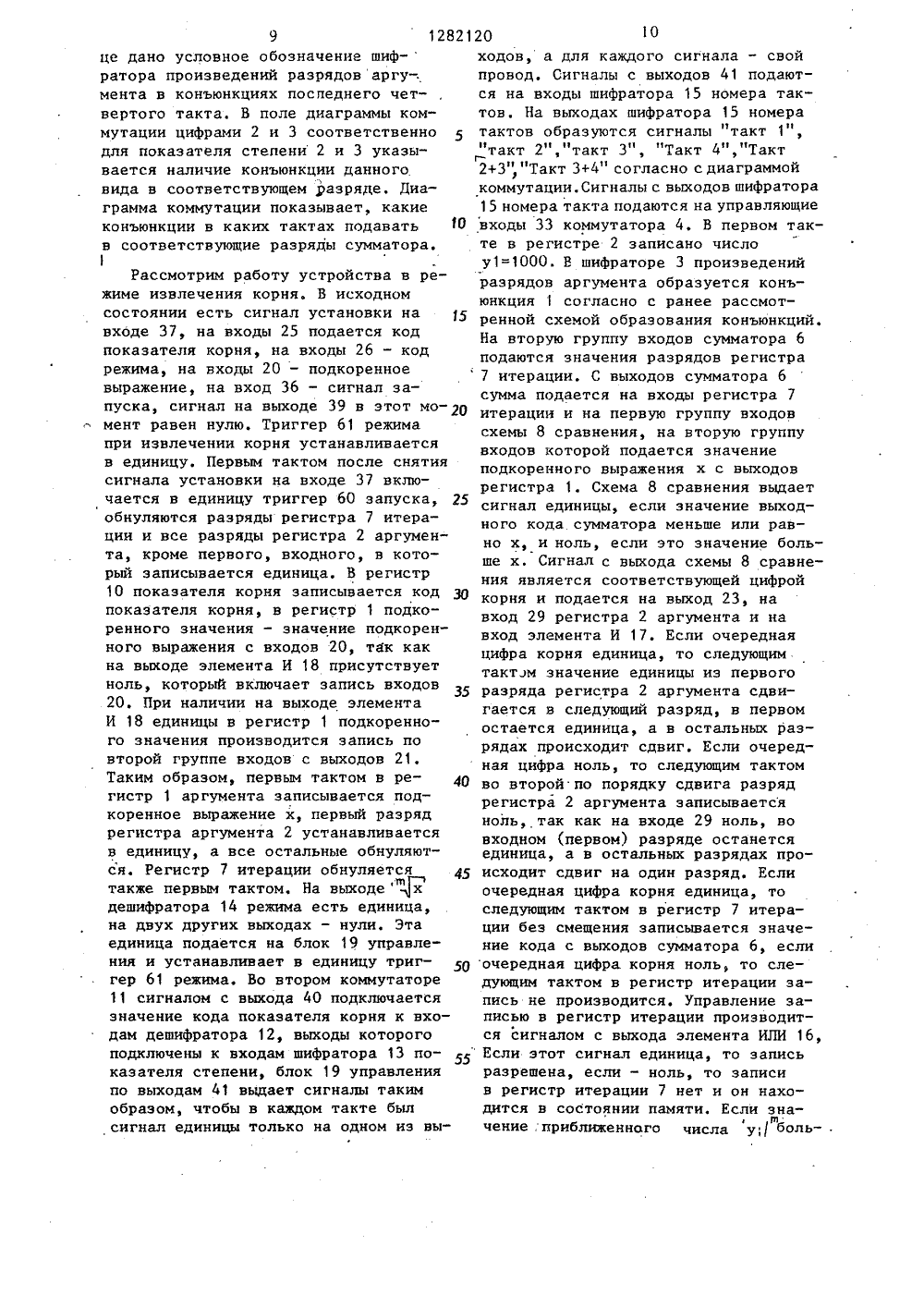

сОки сОВетснихСОЦИАЛИСТ ИЧЕСНИХРЕСПУБЛИК 06 Г 7/5 ный номитет ссОБретениЙ и отнры ГосудАРст ПО ДЕЛАМ АН И ОБРЕТ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССР У 491946, кл, С 06 Г 7/552, 1973.Авторское свидетельство СССР У 1246092, кл. С 06 Р 7/552, 1985. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СТЕПЕН НЫХ ФУНКЦИЙ(57) Устройство может быть применено в специализированных цифровых вычислителях для извлечения корня и возведения в степень двоичных чисел. Устройство позволяет расширить класс решаемых задач за счет возможности вычисления выражений вида х, х х" Устройство содержит регистр подкоренного выражения, регистр аргумента, шифратор произведений разрядов аргумента, первый коммутатор, вход управления записью по первому и второму информационным входам регистра подкоренного значения, сумматор, регистритерации, схему сравнения, регистрпоказателя степени, регистр показателя корня, второй коммутатор, дешифратор, шифратор показателя степени,дешифратор режима, шифратор номератакта, элемент ИЛИ, первый элемент И,второй элемент И, блок управления,вход подкоренного значения устройства,выход результата возведения в степеньустройства, вход аргумента устройства,входы показателя степени корня режимаустройства, информационный вход регистра аргумента, входы сброса, разрешениясдвига, разрешения записи регистрааргумента, выход регистра аргумента, щинформационный, унравляюший входыпервого коммутатора, выход коммутатора,вход запуска, установки в начальное фположение числа тактов устройства, вывыход разрешения вычислений, управле- фния режимом, тактовые входы признакаизвлечения корня и возведения в степень блока управления, 4 ил.Государственн елам изобрете Москва, Ж,670 Подписно комитета СССРий и открытийаушская наб., д. М128212 0 2Регистр аргумента содержит триггеры 44, элементы И 45, элементИ-НЕ 46, элемент 2 И-ИЛИ 47,Коммутатор содержит вход 48 произведений разрядов аргумента, управляющие входы 49 и 50, элементы И 51,элементы ИЛИ 52, выходы 53 разрядовконъюнкции, выход 54 коммутатора.Блок управления содержит генератор 55 тактовых импульсов, регистр56 тактов, элемент И-НЕ 57, коммутатор 58, дешифратор 59 тактов, триггер 60 запуска, триггер 61 режима,элемент ИЛИ 62, элемент И 63.Устройство функционирует следующим образом.Устройство может работатьв трех режимах: извлечения корня х,61 физвлечения корня из числа в п-й стевГпени 1 х , возведения в степень х Изобретение относится к вычислительной технике и может найти применение в специализированных вычислителях для вычисления выражения вида1 х, -х", х , где ш - показатель корня, и - показатель степени.Цель изобретения - расширение класса решаемых задач зй счет возможности вычисления выражения вида фЯ," Р.На фиг.1 представлена функциональная схема устройства; на фиг.2 - пример выполнения регистра аргумента; на фиг.3 - пример выполнения первого коммутатора для коммутации одной из возможных конъюнкций; на фиг.4 - .функциональная схема блока управления. 10 15 Вычисление корня у="Гх производится следующим образом. Сначала предполага-, ется, что первый (старший). значащий разряд корня равен единице, а все остальные в ,нулю, Образуется приближенное число первого такта У 1=0,100 Число у 1 возводится в степень ш и сравнивается со значением х, при этом если ху 1, то у 1=1,если х-( У 11, то У 1=0. Затем образуется приближенное число второго такта У 2=0, У 1=100., которое возводится в ш-ю степень исравнивается с х,причем если ху 2),то у 2=1, если хсу 2, то у 2=0.Для всех остальных тактов производятся аналогичные операции для г-го такта у = =ОуУ 1 У 2, У., 1, которое возводится в ш-ю степень и аналогичным образом сравнивается с х (г - разрядность чисел, выраженных правильными дробями), Последовательность получаемых значений У 1,У 2, , Уесть искомое значение корня.Вычисление 2=,х" производится следующим образом. Сначала число х возводится в степень и, а затем производятся действия по описанному алгоритму, с той разницей, что сравнение очередного значения Е; производися со значением хВозведение числа х производится следующим образом. Рассмотрим диаграмму возведения, в которой использованы числа разрядностью г=4, а показатель степени может принимать значения и= =2,3. Процесс возведения в степень разделен на г=4 тактов. В каждом такте появляется следующий разряд, начиУстройство содержит регистр 1 под коренного значения, регистр, 2 аргумента, шифратор 3 произведений разрядов аргумента, первый коммутатор 4, выход 5 управления записью по первому и второму информационным входам, 25 сумматор 6, регистр 7 итерации, схему 8 сравнения, регистр 9 показателя степени, регистр 10 показателя корня, второй коммутатор 11, дешифратор 12, шифратор 13 показателя степени, дешифратор 14 режима, шифратор 15 номера такта, элемент ИЛИ 6, первый элемент И 17, второй элемент И 18, блок 19 управления, вход 20 подкоренного значения устройства, выход 21 резуль тата возведения в степень устройства, вход 22 аргумента устройства, выход 23 значения корня устройства, входы показателя степени 24, корня 25 режима 26 устройства, информацион ц ный вход 27 регистра аргумента, вход 28 сброса регистра аргумента, вход 29 разрешения сдвига регистра аргумента, вход 30 разрешения записи регистра аргумента, выход 31 регистра 45 аргумента, информационный вход 32 первого коммутатора, управляющие входы 33 и 34 второго коммутатора, выход 35 коммутатора, вход 36 запуска устройства, вход 37 установки в 50 начальное положение устройства, вход 38 числа тактов устройства, выход 38 разрешения вычисления управления записью по первому входу блока управления, выход 40 управления режимом 55 блока управления, тактовый выход 41 блока управления, входы признака извлечения корня 42 и возведения в степень 43 блока управления.Разряд 0 1 2 3 .4 5 6 7 8 9 10 11 12 0 1 2 3 4 О. 1 2 3 4 х 1 1 12 13 14 21 22 23 24 31 32 33 34 41 42 43 44 1 12 13 14 12 2 23 24 13 23 3 34 14 24 34 4 1 такт 2 такт ,3 такт 4 такт 1 этап 12 2 В 2 13 23 314 24 34 О,2 3 4 11 этап 12 12 13 123 13 14 124 134 14 12 12 123 23 23 124 24 234 13 3 1282120 4 ная со старшего.На первом этапе диа- конъюнкция остается без изменения. граммы возведения показано возведение Если конъюнкция не содержит значения числа х в степень 2.1 аккак оба умно- данного разряда, то в нее записываетжаемых числаодинаковы,то конъюнкции ся номер этого разряда х по порядку диаграммы можновидоизменить поранен- .5 номеров. Сумма одинаковых конъюнкций ствам 11=1,21=12,22=",.31=13,32=23, для полученных на втором этапе проме 33=3,41=14,42=24,43=34,44=4,После жуточных совокупностей дает совокуп" суммирования одинаковых конъюнкций ность конъюнкций второго этапа ВЗ,э образуется результатпервого этапаВ 2 сумма конъюнкций которой равна х в виде совокупности определенным об- О Совокупность В 2 состоит из конъюнкций разом расположенных конъюнкций 1,2,2, входящих в состав совокупности ВЗ.13,23,3,14,24,34,4, сумма которых Из взятых по ИЛИ совокупностей В 2 равна х . Умножйм полученную совокуп- и ВЗ можно составить суммарную совоность В 2 на х последовательно разряд купность коньюкций с учетом за разрядом. При умножении какого-ли потактного образования коньюкбо разряда х на конъюнкцию, уже содер- ций совокупностей В 2, жащую значение данного разряда, эта ,ВЗДиаграмма возведения1282120 Диаграмма коммутации шифратор-произведений разрядов аргумента Вид конъюнкции Разряд 0 1 2 3 4 5 6 7 8 9 10 11 12 Такт 2 3 12 34 22 3 3 3 3 13 24 23 2 3 3 3 34 123 123 3,4 14 2 3 3 14 3 3 24 3 3 3 3 34 3 34 3 3 124 134 134 3 3 134 234 234 3 3 Схема ввода Такт 1 2 2 13 Ввод х 3 2 14 4 3 2 1 55 Регистр 2 аргумента Можно заметить, что все конъюнкции предыдущих тактов входят в состав конъюнкций последнего такта. Допустим, что есть регистр 2 аргумента, выхо ды которого соединены с входами шифратора 3 произведений разрядов аргумента, блока элементов И, таким образом, чтобы на выходах последнего были образованы все конъюнкции послед него такта, Разряды регистра 2 аргумента пронумерованы также, как и разряды числа х (старший разряд имеет номер 1 и находится на схеме ввода справа). Пусть в регистр 2 аргу мента со стороны входного разряда вводится число х старшими разрядами вперед, что описывается схемой ввода: В первом такте во входном разряде регистра 2 аргумента записывается разряд 1 числа х, а в остальных разрядах - нули, На месте конъюнкции 4 образуется конъюнкция 1, образование остальных конъюнкций блокировано нулями в других разрядах регистра 2 аргумента. Во втором такте во входной, разряд регистра 2 аргумента записывается разряд 2 числа х, а разряд 1 сдвигается в следующий разряд регистра 2. На месте конъюнкции 4 образуется конъюнкция 2, на месте конъюнкции 34 конъюнкция 12. Аналогично в третьем и четвертом тактах образуются все конъюнкции четвертого такта. Для получения результата возведения в степень нужно просуммировать конъюнкции первого, второго, третьего и четвертого тактов. Для этого нужно в каждом такте подавать конъюнкции на соответствующие разряды сумматора 6..Составим диаграмму коммутации, определяющую подключение конъюнкций к входам сумматора. По горизонтали диаграммы коммутации откладываются разряды, а по вертикали - номера тактов и вид конъюнкций. В правом столб 128219це дано условное обозначение шиф-ратора произведений разрядоваргу-. мента в конъюнкциях последнего четвертого такта. В поле диаграммы коммутации цифрами 2 и 3 соответственно для показателя степени 2 и 3 указывается наличие конъюнкции данного вида в соответствующем разряде. Диаграмма коммутации показывает, какие конъюнкции в каких тактах подавать 10 в соответствующие разряды сумматора.Рассмотрим работу устройства в режиме извлечения корня, В исходном состоянии есть сигнал установки на входе 37, на входы 25 подается код показателя корня, на входы 26 - код режима, на входы 20 - подкоренное выражение, на вход 36 - сигнал запуска, сигнал на выходе 39 в этот момент равен нулю, Триггер 61 режима при извлечении корня устанавливается в единицу. Первым тактом после снятия сигнала установки на входе 37 включается в единицу триггер 60 запуска, 25 обнуляются разряды регистра 7 итерации и все разряды регистра 2 аргумента, кроме первого, входного, в который записывается единица. В регистр 10 показателя корня записывается код З 0 показателя корня, в регистр 1 подкоренного значения - значение подкоренного выражения с входов 20, так как на выходе элемента И 18 присутствует ноль, который включает запись входов 20. При наличии на выходе элемента И 18 единицы в регистр 1 подкоренного значения производится запись по второй группе входов с выходов 21, Таким образом, первым тактом в ре гистр 1 аргумента записывается подкоренное выражение х, первый разряд регистра аргумента 2 устанавливается в единицу, а все остальные обнуляются. Регистр 7 итерации обнуляется также первым тактом. На выходе -х дешифратора 14 режима есть единица, на двух других выходах - нули. Эта единица подается на блок 19 управления и устанавливает в единицу триггер 61 режима, Во втором коммутаторе 11 сигналом с выхода 40 подключается значение кода показателя корня к входам дешифратора 12, выходы которого подключены к входам шифратора 13 по казателя степени, блок 19 управления по выходам 41 вьщает сигналы таким образом, чтобы в каждом такте был сигнал единицы только на одном из вы 20 10ходов, а для каждого сигнала - свой провод. Сигналы с выходов 41 подаются на входы шифратора 15 номера тактов. На выходах шифратора 15 номера тактов образуются сигналы "такт 1", "такт 2","такт 3", "Такт 4","Такт 2+3","Такт 3+4" согласно с диаграммой коммутации. Сигналы с выходов шифратора 15 номера такта подаются на управляющие входы 33 коммутатора 4, В первом такте в регистре 2 записано число у 1=1000. В шифраторе 3 произведений разрядов аргумента образуется коньюнкция 1 согласно с ранее рассмотренной схемой образования конъюнкций, На вторую группу входов сумматора 6 подаются значения разрядов регистра 7 итерации. С выходов сумматора 6 сумма подается на входы регистра 7 итерации и на первую группу входов схемы 8 сравнения, на вторую группу входов которой подается значение подкоренного выражения х с выходов регистра 1. Схема 8 сравнения вьщает сигнал единицы, если значение выходного кода сумматора меньше или равно х, и ноль, если это значение больше х, Сигнал с выхода схемы 8 сравнения является соответствующей цифрой корня и подается на выход 23, на вход 29 регистра 2 аргумента и на вход элемента И 17. Если очередная цифра корня единица, то следующим тактэм значение единицы из первого разряда регистра 2 аргумента сдвигается в следующий разряд, в первом остается единица, а в остальных разрядах происходит сдвиг. Если очередная цифра ноль, то следующим тактом во второй по порядку сдвига разряд регистра 2 аргумента записывается ноль, так как на входе 29 ноль, во входном (первом) разряде останется единица, а в остальных разрядах происходит сдвиг на один разряд. Если очередная цифра корня единица, то следующим тактом в регистр 7 итерации без смещения записывается значение кода с выходов сумматора 6, если очередная цифра корня ноль, то следующим тактом в регистр итерации запись не производится. Управление записью в регистр итерации производится сигналом с выхода элемента ИЛИ 16, Если этот сигнал единица, то запись разрешена, если - ноль, то записи в регистр итерации 7 нет и он находится в состоянии памяти. Если знау Вчение,приближенного числа у, боль12821ше подкоренного выражения, то изменения содержимого регистра итерации не происходит.Подача значений конъюнкций очередных тактов на входы сумматора 6 про- .5 изводится с помощью коммутатора 4 согласно с диаграммой коммутации.Для рассматриваемого примера в последнем четвертом такте образуются конъюнкции 4,34,24,234,134,124. Первый (входной) разряд регистра 2 аргумента в этих обозначениях имеет номер 4, следующий - номер 3 и т.д., согласно с представленной ранее схемой ввода. С выходов шифратора 3 произведений разрядов аргумента значения конъюнкции подаются на входы 32 коммутатора 4, который построен согласно с диаграммой коммутации. На один из входов каждого элемента И коммутатора 4 подается значение соответствующей конъюнкции с выхода шифратора 3, на второй вход - сигнал управления соответствующего такта, в котором данная конъюнкция под 25 ключается к входу сумматора 6 данно го разряда, на третий вход подается1 сигнал, обозначающий показатель корня или степени. Выходы элементов И являются выходами 35 соответствующих 30 разрядов коммутатора 4. Если эначе 1ние сумматора. меньше или. равно х, то вторым тактом производится запись значения выходного кода сумматора 6 в регистр 7 итерации и сдвиг в ре гистре 2 с записью единицы во входной разряд. С выходов регистра 7 итерации на входы сумматора 6 подается сумма предыдущего такта, где суммируется с конъюнкциями второго такта, На выходах сумматора 6 образуется сумма второго такта, которая .сравнивается со значением х на схеме сравнения. Результат извлечения корня получается на выходе 23 последо-. 45 вательно старшими разрядами вперед, Второй коммутатор 11 переключает значения показателей корня и степени с выходов регистров 10 и 9 по сигналу с выхода триггера 61 режима 50 блока 19 управления. Если триггер 61 в единице, то передается код показателя корня, если в нуле, то - код показателя степени.55В режиме возведения в степеньчисла х,на входах 26 устанавливаетсякод режима возведения в степень.Триггер 61 режима сигналом с выхода 2012возведения в степень дешифратора 14 режима устанавливается в ноль, на входе разрешения записи регистра, 7 итераций, постоянно присутствует единица, и каждым тактом в него записывается код с выходов сумматора 6, При значении триггера 61 режима ноль регистр 2 аргумента работает на последовательный ввод числа х, подаваемого по входу 22 старшими разрядами вперед, где старший разряд х подается при нулевом значении на выходе 39 и первым тактом записывается в регистр 2 аргумента. Образование .конъюнкций в тактах и подача их на сумматор 6 производится также, как и при извлечении корня, с той разницей, что выходное значение сумматора 6 записывается в регистр 7 итераций каждым тактом и не зависит от выходного сигнала схемы 8 сравнения. Результат возведения в степень записывается в регистр 7 по г+1 такту и подается на выходы 21. В режиме вычисления корня из числа х в и-й степени сначала производится возведение числа х в степень эа первый цикл в г+1 тактов при значении триггера 61 режима, равном нулю. Затем во втором цикле из г+1 тактов при значении триггера 61 режима, равном единице, производится вычисление корня ш-й степени из числа х . При этом по первому такту второго цикла результат возведения в степень х с выходов регистраи7 итераций записывается во второй группе входов в регистр 1 подкоренного значения, Затем во втором цикле производится процесс извлечения корня из числа х , а сравнение выходного значения сумматора 6 производится не с х, а с х . Результат выдается последовательно старшими разрядами вперед по выхоцу 23.Работа блока 19 управления. По шинам 38 на блок 19 управления подается код разрядности, который поступает на дешифратор 59 тактов. Выходы дешифратора 59 тактов соединены с управляющими входами коммутатора 58, чем определяется подключение соответствующего разряда регистра - распределителя 56 к выходу коммутатора 58, Пусть триггер 60 запуска и регистр 56 тактов в нуле. Первым тактом после снятия сигнала установки включается в единицу триггер 60 запуска, на выходе 23 образуется первый разрядУстройство для вычисления степен- ф 45 ных функций, содержащее регистр аргумента, дешифратор, шифратор показателя степени, сумматор, шифратор произведений разрядов аргумента и первый коммутатор, причем выходы дешифратора 50 соединены с входами шифратора показателя степени, выходы которого соединены с управляющими входами первого коммутатора, информационные входы ко- . торого соединены с выходами шифрато ра произведений разрядов аргумента, входы котороо соединены с выходами разрядов регистра аргумента, о т - л и ч а ю щ е е с я тем, что, с це 13 12821 корня, Вторым тактом в первый разряд регистра 56 записывается единица, на выходе 23 образуется второй разряд корня, Далее единица продвигается в регистре 56 каждым следующим тактом до тех пор, пока она не появится на выходе коммутцуора 58 в виде г-состояния, которое подается на К-вход триггера 60 запуска и на С- вход триггера 1 режима. По г+1 такту 10 триггер 60 запуска переходит в ноль, обнуляется регистр 56 тактов, следующим тактом начинается новый цикл. Триггер 61 в режиме извлечения корня постоянно включен в единицу, а в ре жиме возведения в степень - в ноль. Режим извлечения корня из числа в степени и содержит два цикла - цикл возведения в степень, при котором триггер 61 режима в нуле, и цикл из влечения корня, при котором триггер 61 режима в единице. Триггер 61 переключается в единицу после окончания первого цикла отрицательным фронтом г-состояния с выхода коммутатора 58, т,е. под действием г+1 такта. При первом такте второго цикла будет уже режим извлечения корня, аналогично при переключении триггера 61 режима из единицы в ноль. При смене 30 режимов из режима извлечения корня в режим извлечения корня из числа в степени нужно предварительно подать сигнал установки на вход 37 или провести смену через подачу кода режима возведения в степень с тем расчетом, чтобы триггер 61 режима в исходном состоянии бып в нуле. .При всех остальных переходах из режима в режим достаточно установки кода 40 режима на входах 26. формула изобретения го1 члью расширения класса решаемых задач за счет вычисления корня ш-степени, в него дополнительно введены регистр показателя корня, второй коммутатор, дешифратор режима, шифратор номера такта, схема сравнения, регистр итераций, регистр подкоренного значения, два элемента И, элемент ИЛИ и блок управления, причем входы значений показателя степени и показателя корня устройства соединены с информационными входами регистра показателя степени и регистра показателя корня соответственно, выходы регистра показателя степени и регистра показателя корня соединены с первым и вторым информационными входами второго коммутато ра соответственно, выход второго коммутатора соединен с входом дешифратора, управляющий вход второго коммутатора соединен с входом разрешения записи регистра аргумента, с первым входом первого элемента И, с первым инверсным входом элемента ИЛИ и с выходом управления режимом блока управления, выход разрешения вычисления которого соединен с входами разрешения записи регистра подкоренного значения, регистра итерации, регистра- показателя степени, регистра показателя корня и входом сброса регистра аргумента, вход разрешения сдвига которого соединен с выходом схемысравнения, первый вход которой соединен с выходом сумматора, второй вход схемы сравнения соединен с выходом регистра подкоренного значения, первый и второй информационные входы которого соединены с выходами регистра итерации и входом подкоренногозначения устройства соответственно,вход управления записью по первому и второму информационным входам регистра подкоренного значения соединен с выходом второго элемента И, первый, вход которого соединен с выходом признака извлечения корня дешифратора режима, второй вход второго элемента И соединен с выходом управления режимом блока управления, тактовый выход которого соединен с входом шифратора номера такта, выход которогосоединен с управляющим выходом первого коммутатора, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом регистра итерации, вход разрешения записи которого соединен с выходом эле 15 12821 мента ИЛИ, второй вход которого соединен с выходом первого элемента И, входы установки в начальное состояние запуска и числа тактов блока управления являются одноименными входа-,5 ми устройства, входы задания режима извлечения корня и возведения в степень блока управления соединены с соответствующими выходами дешифратора режима, вход которого является 10 входом задания режима устройства, выход значения корня устройства соединен с выходом схемы сравнения, вход аргумента устройства подключен к информационному входу регистра аргумен та, выход результата возведения в степень устройства соединен с выходом регистра итерации, причем блок управления содержит триггер запуска, триггер режима, регистр тактов, де шифратор тактов, коммутатор, элемент И, элемент ИЛИ, элемент И-НЕ и генератор тактовых импульсов, при,чем вход числа тактов блока управления соединен с входом дешифратора тактов, вход которого соединен с управляющим входом коммутатора, информационные входы которого соединены )с выходами разрядов регистра тактов 30 с тактовым выходом блока управления и входами элемента И-НЕ, выход которого соединен с последовательным информационным входом регистра тактов,20 16вход сброса которого соединен с гыходом триггера запуска и выходом разрешения вычислений блока управления,вход установки в начальное состояниекоторого соединен с входом сбросатриггера установки, 1 н К входы которого соединены соответственно с входом запуска блока управления и выходом коммутатора, входы кодов операцийизвлечения корня и возведения в степень блока управления соединены соответственно с входами сброса триггерарежима и первым входом элемента ИЛИблока управления, второй вход которого соединен с выходом элемента И блока управления, первый инверсный ивторой входы которого соединены с входом кода операции извлечения корняблока управления и входом установкив начальное положение блока управле-,ния соответственно, выход триггерарежима является выходом управлениярежимом блока управления, инверсныйвыход триггера режима соединен с информационным входом этого триггера,а инверсный синхроннзирующий вход соесоединен с вьжодом коммутатора, выходгенератора тактовых импульсов соеди-нен с синхроннзирующими входами регистра показателя степени, регистрапоказателя корня, регистра аргумента,регистра промежуточного значения, регистра подкоренного значения и регистра тактовых импульсов.

СмотретьЗаявка

3841879, 09.01.1985

ГЛАЗАЧЕВ АЛЕКСАНДР ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, степенных, функций

Опубликовано: 07.01.1987

Код ссылки

<a href="https://patents.su/11-1282120-ustrojjstvo-dlya-vychisleniya-stepennykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления степенных функций</a>

Предыдущий патент: Устройство для возведения в степень

Следующий патент: Мультимикропрограммное устройство управления

Случайный патент: Устройство для бурения скважин под набивные сваи