Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1786671

Автор: Неволин

Текст

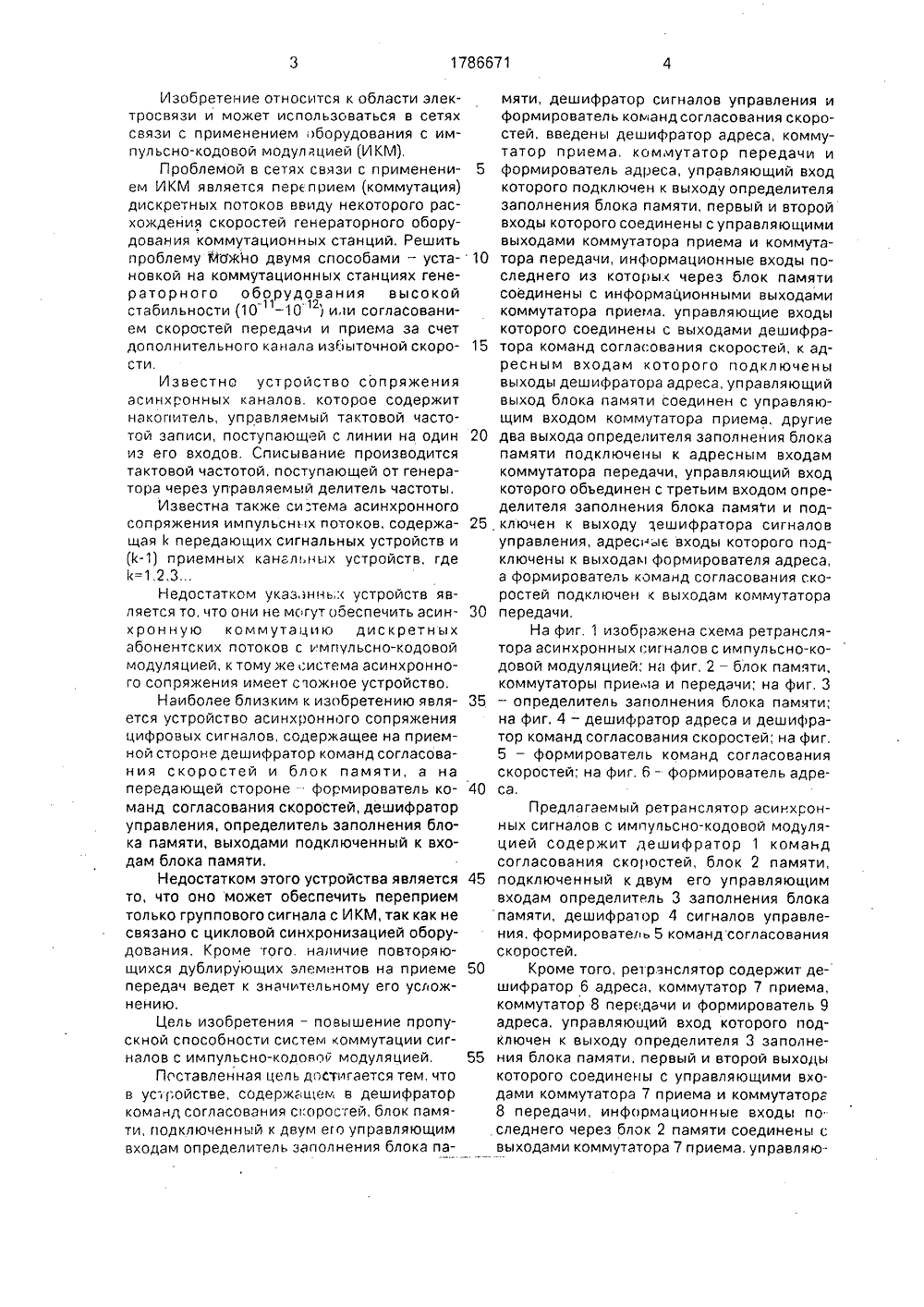

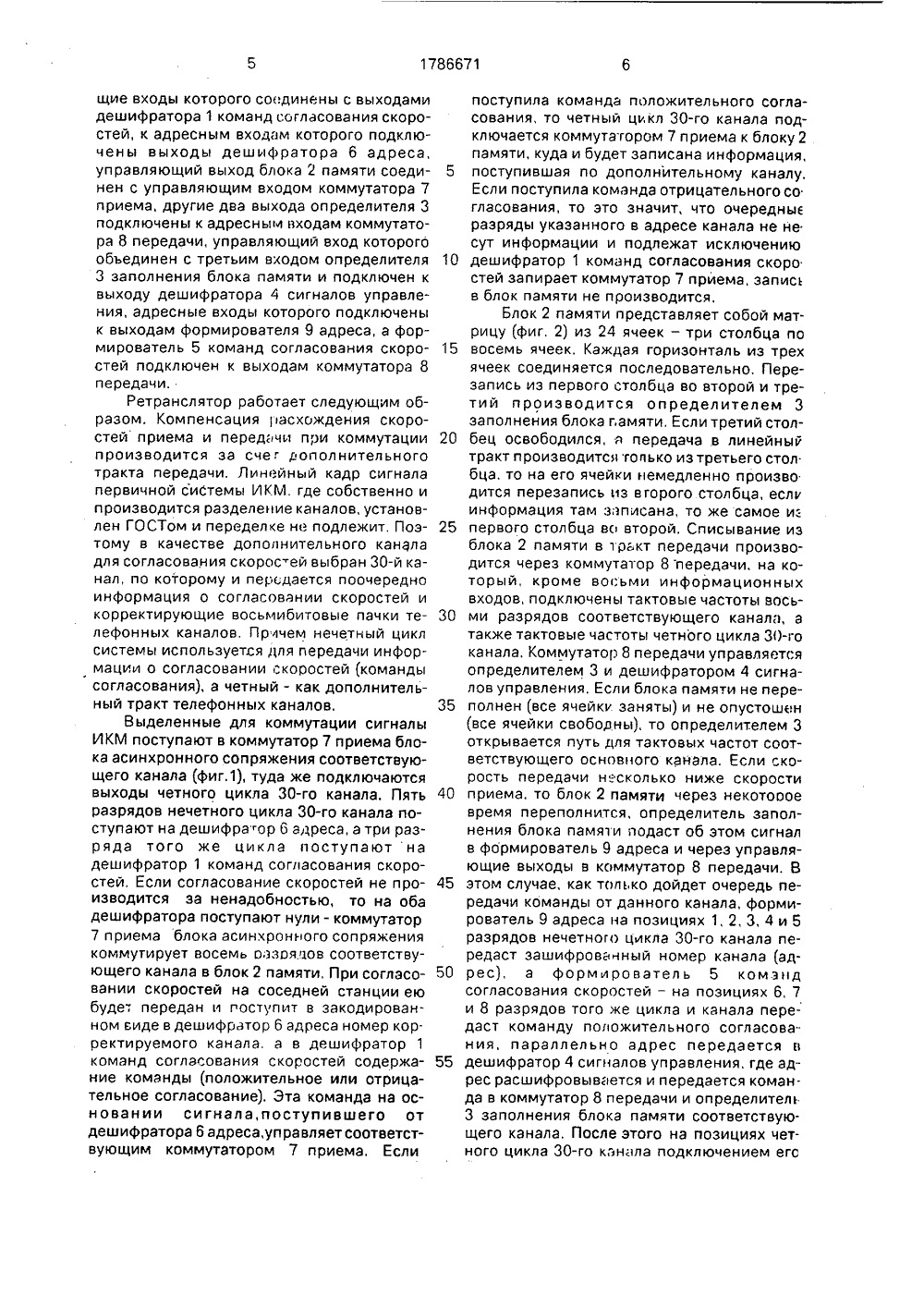

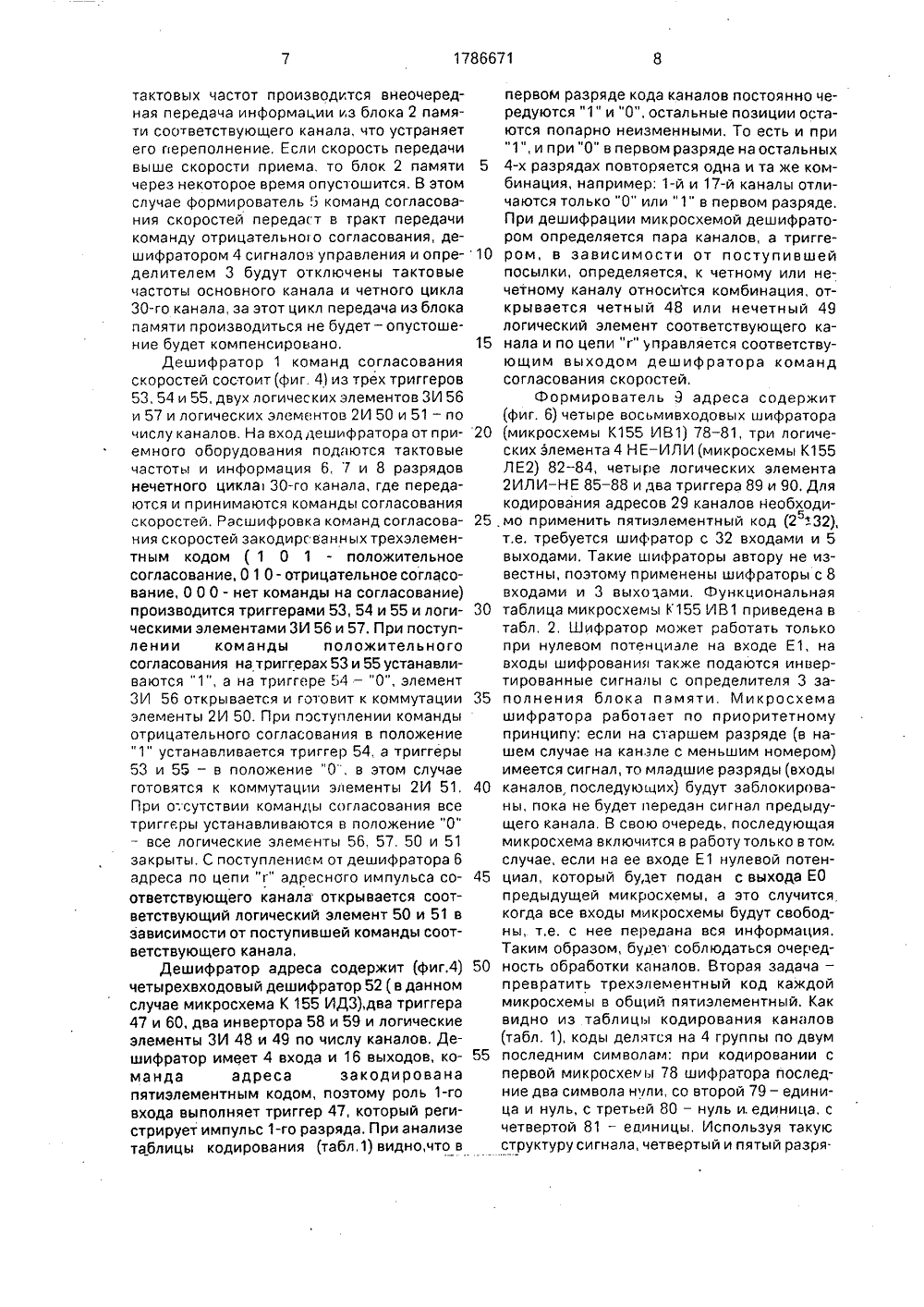

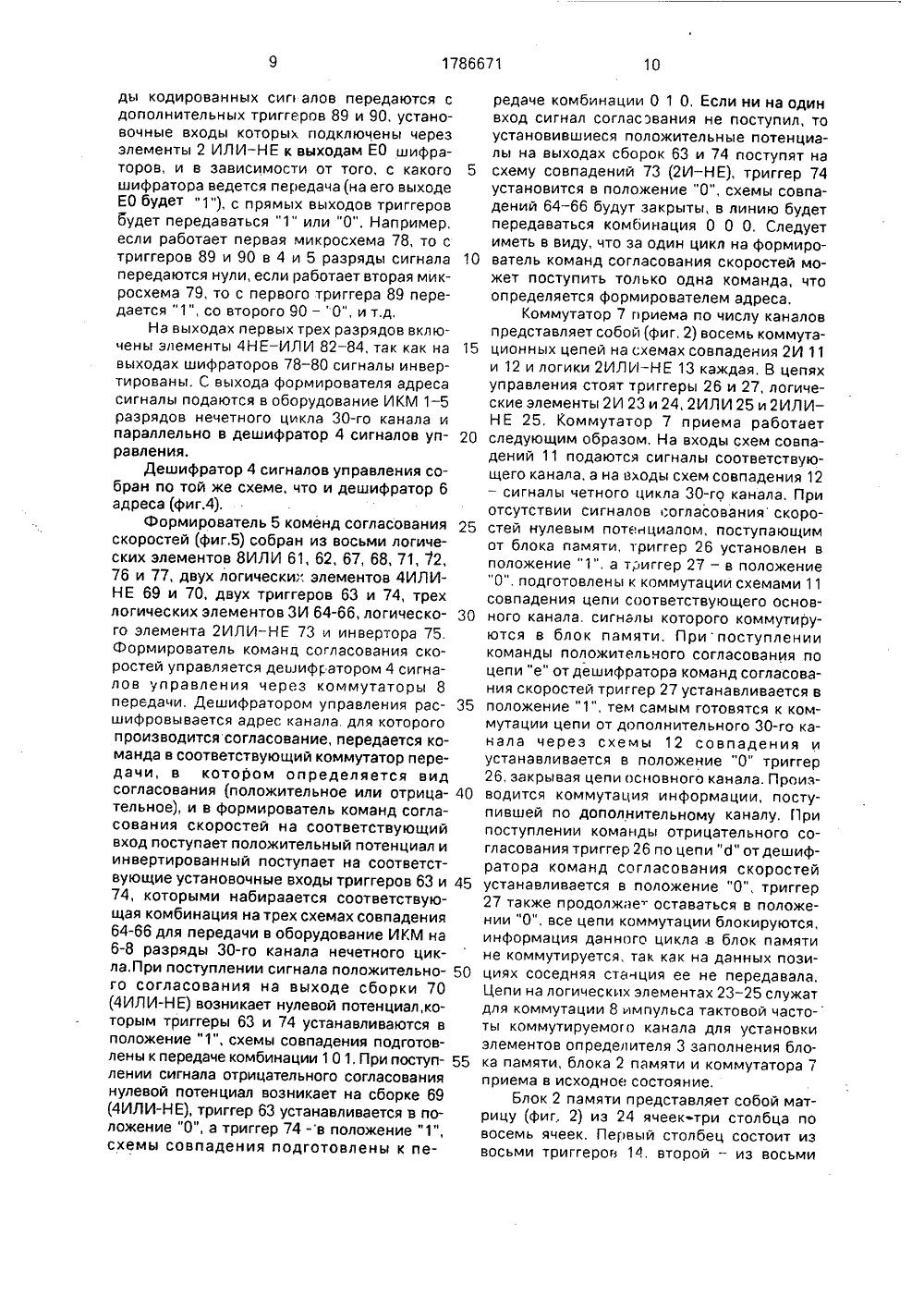

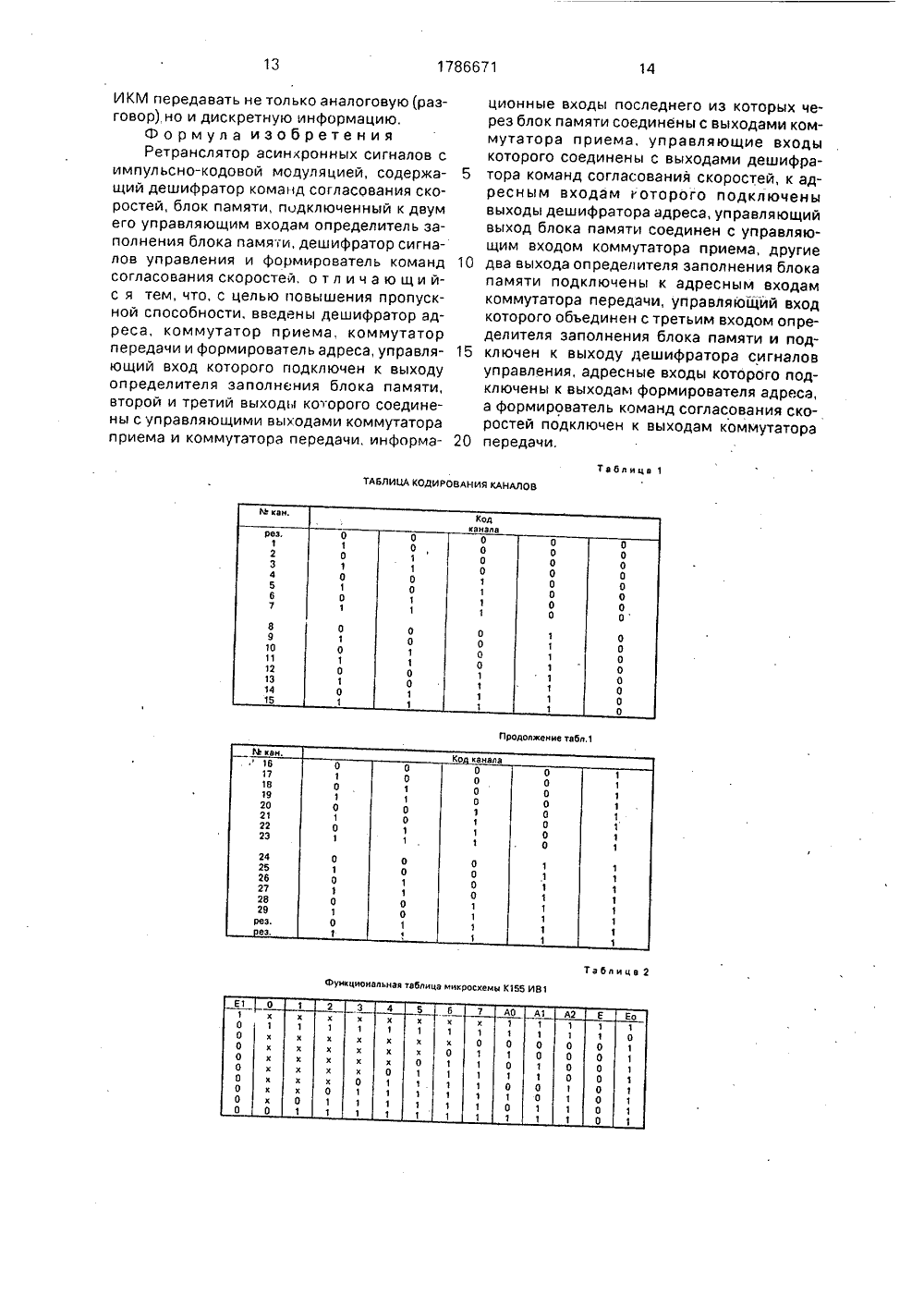

СО ЮЗ СЭ В.". ТС КИХСОЦИАЛ ИС; ИЧЕСКРЕСПУБЛИК 17 6 9) (11) А 4,3 3/О БРЕТЕНИЯ СБ ИДЕТ 8 33415/09(57 Из рет эан пуг.сн исп).ль изоб )е(21) 48 (22) 30 СИТСЯ К нных си сследовател ьи научзи кий72) Н СС 81 60 Р АСИНХРОННЫХ СИГСНО-КОДОВОЙ МОДУРАНСЛС ИМП4(54) Р НАЛ ЛЛЦ СО Ь ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) ПИСАНИЕ рское свидетельс б, кл. Н 04 Л 3/06 блок . блока равлен вания ком мут чи и ф 3 - 2 - 7,обретение относляции асинхроо-кодовой м)дуляцией изавано в электросвязтения: устройство содер1 команд согласованипамяти, определитель 3 )амяти. дешифратор 4 1 я, форми роваель 5.комскоростей, дещифратоатор 7 приема коммута ормирователь 9 адреса3-8 - 5, 9 - 4 - 8. б ил. устроиствам налов с имможет бытьСущность жит дешифскоростей, заполнения сигналов упанд согласор б адреса, ор 3 передаб - 1 - 7 - 2 - 8,Составитель Н.НеволиТехред М,Моргентал Тираж Государственного комитета по изобреПодписноениям и открытиям при ГКНТ ССС я наб 4/5Изобретение относится к области электросвязи и может использсваться в сетяхсвязи с применением оборудования с импул ьс но-кодовой модул я ци ей (И КМ),Проблемой в сетях связи с применением ИКМ является переприем (коммутация)дискретных потоков ввиду некоторого расхокдения скоростей генераторного оборудования коммутационных станций, Решитьпроблему можно двумя способами - установкой на коммутационных станциях генераторного оборудования высокойстабильности (10 - 10или согласовани 1 г,ем скоростей передачи и приема за счетдополнительного канала избыточной скорости.Известно устройство сопряженияасинхронных каналов. которое содержитнакопитель, управляемый тактовой частотой записи, поступающзй с линии на одиниз его входов. Списывание производитсятактовой частотой, поступающей от генератора через управляемый делитель частоты,Известна также си:тема асинхронногосопряжения импульсных потоков, содержащая 1 передающих сигнальных устройств и(1-1) приемных канальных устройств, где1=1,2,3Недостатком указанньс устройств является то, что они не мс гут обеспечить асинхронную коммутацию дискретныхабонентских потоков с импульсно-кодовоймодуляцией, к тому же система асинхронного сопряжения имеет сложное устройство.Наиболее близким к изобретению является устройство асинхронного сопряженияцифровых сигналов, содержащее на приемной стороне дешифратор команд согласования скоростей и блок памяти, а напередающей сторонеформирователь команд согласования скоростей, дешифраторуправления, определитель заполнения блока памяти, выходами подключенный к входам блока памяти,Недостатком этого устройства являетсято, что оно может обеспечить переприемтолько группового сигнала с ИКМ, так как несвязано с цикловой синхронизацией оборудования. Кроме того. наличие повторяющихся дублирующих элементов на приемепередач ведет к значительному его усложнению,Цель изобретения - повышение пропускной способности систем коммутации сигналов с импульсно-кодовоР модуляцией,Поставленная цель достигается тем, чтов ус- ройстве, содержащем в дешифраторкоманд согласования скоростей, блок памяти, подключенный к двум ео управляющимвходам определитель заполнения блока па 5 10 15 20 25 ключен к выходу ешифратора сигналов 30 35 40 45 50 55 мяти, дешифратор сигналов управления и формирователь команд согласования скоростей, введены дешифратор адреса, коммутатор приема, коммутатор передачи и формирователь адреса, управляющий вход которого подключен к выходу определителя заполнения блока памяти, первый и второй входы которого соединены с управляющими выходами коммутатора приема и коммутатора передачи, информационные входы последнего из которых через блок памяти соединены с информационными выходами коммутатора приема, управляющие входы которого соединены с выходами дешифратора команд согласования скоростей, к адресным входам которого подключены выходы дешифратора адреса, управляющий выход блока памяти соединен с управляющим входом коммутатора приема, другие два выхода определителя заполнения блока памяти подключены к адресным входам коммутатора передачи, управляющий вход которого объединен с третьим входом определителя заполнения блока памяти и подуправления, адрес 1 ые входы которого подключены к выходам формирователя адреса, а формирователь команд согласования скоростей подключен к выходам коммутатора передачи. На фиг. 1 изображена схема ретранслятора асинхронных сигналов с импульсно-кодовой модуляцией; на фиг, 2 - блок памяти, коммутаторы прие а и передачи; на фиг, 3 - определитель заполнения блока памчти; на фиг. 4 - дешифратор адреса и дешифратор команд согласования скоростей; на фиг, 5 - формирователь команд согласования скоростей; на фиг. 6 - формирователь адреса,Предлагаемый ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией содержит дешифратор 1 команд согласования скоростей, блок 2 памяти, подключенный к двум его управляющим входам определитель 3 заполнения блока памяти, дешифра 1 ор 4 сигналов управления, формирователь 5 команд согласования скоростей,Кроме того, ретранслятор содержит дешифратор 6 адреса, коммутатор 7 приема, коммутатор 8 передачи и формирователь 9 адреса, управляющий вход которого подключен к выходу определителя 3 заполнения блока памяти, первый и второй выходы которого соединены с управляющими входами коммутатора 7 приема и коммутатора 8 передачи, информационные входы по следнего через блок 2 памяти соединены с выходами коммутатора 7 приема, управляю5 10 15 20 25 30 35 40 45 50 55 щие входы которого соединены с выходами дешифратора 1 команд согласования скоростей, к адресным входам которого подключены выходы дешифратора 6 адреса, управляющий выход блока 2 памяти соединен с управляющим входом коммутатора 7 приема, другие два выхода определителя 3 подключены к адресным входам коммутатора 8 передачи, управляющий вход которого объединен с третьим входом определителя 3 заполнения блока памяти и подключен к выходу дешифратора 4 сигналов управления, адресные входы которого подключены к выходам формирователя 9 адреса, а формирователь 5 команд согласования скоростей подключен к выходам коммутатора 8 передачи,Ретранслятор работает следующим образом. Компенсация расхождения скоростей приема и передачи при коммутации производится за счег дополнительного тракта передачи, Линейньй кадр сигнала первичной системы ИКМ. где собственно и производится разделение каналов, установлен ГОСТом и переделке не подлежит. Поэтому в качестве дополнительного канала для согласования скорос"ей выбран 30-й канал, по которому и передается поочередно информация о согласовании скоростей и корректирующие восьмибитовые пачки телефонных каналов. Причем нечетный цикл системы используется для передачи информации о согласовании скоростей (команды согласования), а четный - как дополнительный тракт телефонных каналов,Выделенные для коммутации сигналы ИКМ поступают в коммутатор 7 приема блока асинхронного сопряжения соответствующего канала (фиг,1), туда же подключаются выходы четного цикла 30-го канала, Пять разрядов нечетного цикла 30-го канала поступают на дешифраор б адреса, а три разряда того же цикла поступают на дешифратор 1 команд согласования скоростей, Если согласование скоростей не производится эа ненадобностью, то на оба дешифратора поступают нули - коммутатор 7 приема блока асинхронного сопряжения коммутирует восемь оазоядов соответствующего канала в блок 2 памяти, При согласовании скоростей на соседней станции ею буде", передан и поступит в закодированном виде в дешифратор б адреса номер корректируемого канала. а в дешифратор 1 команд согласования скоростей содержание команды (положительное или отрицательное согласование), Эта команда на основании сигнала, поступившего от дешифратора 6 адреса,управляет соответствующим коммутатором 7 приема, Если поступила команда положительного согласования, то четный цикл 30-го канала подключается коммутатором 7 приема к блоку 2 памяти, куда и будет записана информация, поступившая по дополнительному каналу. Если поступила команда отрицательного со гласования, то это значит, что очередные разряды указанного в адресе канала не не. сут информации и подлежат исключению дешифратор 1 команд согласования скоро. стей запирает коммутатор 7 приема, запис в блок памяти не производится,Блок 2 памяти представляет собой матрицу (фиг. 2) из 24 ячеек - три столбца по восемь ячеек, Каждая горизонталь из трех ячеек соединяется последовательно, Перезапись из первого столбца во второй и третий производится определителем 3 заполнения блока г,амяти, Если третий столбец освободился, в передача в линейный тракт производится только из третьего стол. бца, то на его ячейки немедленно произво дится перезапись из вгорого столбца, есл информация там записана, то же самое и:. первого столбца во второй. Списывание из блока 2 памяти в тракт передачи производится через коммутатор 8 передачи, на который, кроме восьми информационных входов, подключены тактовые частоты восьми разрядов соответствующего канала, а также тактовые частоты четного цикла 30-го канала. Коммутатор 8 передачи управляется определителем 3 и дешифратором 4 сигналов управления, Если блока памяти не переполнен (все ячейки заняты) и не опустошен все ячейки своборны), то определителем 3 открывается путь для тактовых частот соответствующего основного канала. Если скорость передачи несколько ниже скорости приема, то блок 2 памяти через некотооое время переполнится, определитель заполнения блока памяти подаст об этом сигнал в формирователь 9 адреса и через управляющие выходы в коммутатор 8 передачи. В этом случае, как только дойдет очередь передачи команды от данного канала, формирователь 9 адреса на позициях 1, 2, 3, 4 и 5 разрядов нечетного цикла 30-го канала передаст зашифрованный номер канала (адрес), а формирователь 5 ком энд согласования скоростей - на позициях б, 7 и 8 разрядов того же цикла и канала передаст команду положительного согласования, параллельно адрес передается в дешифратор 4 сигналов управления, где адрес расшифровывается и передается команда в коммутатор 8 передачи и определитель 3 заполнения блока памяти соответствующего канала. После этого на позициях четного цикла 30-го канала подключением еготактовых частот производится внеочередная передача информации из блока 2 памяти соответствующего канала, что устраняет его переполнение, Если скорость передачи выше скорости приема. то блок 2 памяти через некоторое время опустошится, В этом случае формирователь 5 команд согласования скоростей передагт в тракт передачи команду отрицательноо согласования, дешифратором 4 сигналов управления и определителем 3 будут отключены тактовые частоты основного канала и четного цикла 30-го канала, за этот цикл передача из блока памяти производиться не будет - опустошение будет компенсировано.Дешифратор 1 команд согласования скоростей состоит (фиг. 4) из трех триггеров 53, 54 и 55, двух логических элементов ЗИ 56 и 57 и логических элементов 2 И 50 и 51 - по числу каналов. На входдешифратора от приемного оборудования подаются тактовые частоты и информация б. 7 и 8 разрядов нечетного цикла 30-го канала, где передаются и принимаются команды согласования скоростей. Расшифровка команд согласования скоростей закодирс ванных трехэлементным кодом ( 1 0 1 - положительное согласование, 0 1 0 - отрицательное согласование, 0 0 0 - нет команды на согласование) производится триггерами 53, 54 и 55 и логическими элементами ЗИ 56 и 57. При поступлении команды положительного согласования на триггерах 53 и 55 устанавливаются "1", а на триггере 54 - "0", элемент ЗИ 56 открывается и готовит к коммутации элементы 2 И 50, При поступлении команды отрицательного согласования в положение "1" устанавливается триггер 54, а триггеры 53 и 55 - в положение "0", в этом случае готовятся к коммутации элементы 2 И 51, При о;сутствии команды согласования все триггеры устанавливаются в положение "0" - все логические элементы 56. 57. 50 и 51 закрыты. С поступлением от дешифратора б адреса по цепи "г" адресного импульса соответствующего канала открывается соответствующий логический элемент 50 и 51 в зависимости от поступившей команды соответствующего канала,Дешифратор адреса содержит (фиг.4) четырехвходовый дешифратор 52 (в данном случае микросхема К 155 ИДЗ),два триггера 47 и 60, два инвертора 58 и 59 и логические элементы ЗИ 48 и 49 по числу каналов. Дешифратор имеет 4 входа и 16 выходов, команда адреса закодирована пятиэлементным кодом, поэтому роль 1-го входа выполняет триггер 47, который регистрирует импульс 1-го разряда, При анализе таблицы кодирования (табл,1) видно,что в5 10 20 ских элемента 4 НЕ - ИЛИ (микросхемы К 155 ЛЕ 2) 82 - 84, четыре логических элемента 2 ИЛИ - НЕ 85 - 88 и два триггера 89 и 90, Для кодирования адресов 29 каналов необходи мо применить пятиэлементный код (2 ф 32),т.е. требуется шифратор с 32 входами и 5 выходами, Такие шифраторы автору не известны, поэтому применены шифраторы с 8 входами и 3 выходами, Функциональная 30 35 40 45 50 55 первом разряде кода каналов постоянно чередуются "1" и "0", остальные позиции остаются попарно неизменными. То есть и при "1", и при "0" в первом разряде на остальных 4-х разрядах повторяется одна и та же комбинация, например: 1-й и 17-й каналы отличаются только "0" или "1" в первом разряде. При дешифрации микросхемой дешифратором определяется пара каналов, а триггером, в зависимости от поступившей посылки, определяется, к четному или нечетному каналу относится комбинация, открывается четный 48 или нечетный 49 логический элемент соответствующего канала и по цепи "г" управляется соответствующим выходом дешифратора команд согласования скоростей,Формирователь д адреса содержит (фиг. 6) четыре восьмивходовых шифратора (микросхемы К 155 ИВ 1) 78 - 81, три логичетаблица микросхемы К 155 ИВ 1 приведена в табл, 2. Шифратор может работать только при нулевом потенциале на входе Е 1, на входы шифрования также подаются инвертированные сигналы с определителя 3 заполнения блока памяти, Микросхема шифратора работает по приоритетному принципу: если на старшем разряде (в нашем случае на канале с меньшим номером) имеется сигнал, то младшие разряды (входы каналов, последующих) будут заблокированы, пока не будет передан сигнал предыдущего канала, В свою очередь, последующая микросхема включится в работу только в том случае, если на ее входе Е 1 нулевой потенциал, который будет подан с выхода ЕО предыдущей микросхемы, а это случится когда все входы микросхемы будут свободны, т,е. с нее передана вся информация, Таким образом, буде 1 соблюдаться очередность обработки каналов, Вторая задача - превратить трехэлементный код каждой микросхемы в общий пятиэлементный. Как видно из таблицы кодирования каналов (табл, 1), коды делятся на 4 группы по двум последним символам: при кодировании с первой микросхемы 78 шифратора последние два символа нули, со второй 79 - единица и нуль, с третьей 80 - нуль и. единица, с четвертой 81 - единицы, Используя такую структуру сигнала, четвертый и пятый разря.5 10 15 20 25 30 35 40 45 50 55 ды кодированных сип алов передаются с дополнительных триггеров 89 и 90, установочные входы которых подключены через элементы 2 ИЛИ - НЕ к выходам ЕО шифраторов, и в зависимости от того, с какого шифратора ведется передача(на его выходе ЕО будет "1"), с прямых выходов триггеров будет передаваться "1" или "0", Например, если работает первая микросхема 78, то с триггеров 89 и 90 в 4 и 5 разряды сигнала передаются нули, если работает вторая микросхема 79, то с первого триггера 89 передается "1", со второго 90 -0", и т,д,На выходах первых трех разрядов включены элементы 4 НЕ - ИЛИ 82 - 84, тэк как на выходах шифраторов 78 - 80 сигналы инвертированы. С выхода формирователя адреса сигналы подаются в оборудование ИКМ 1 - 5 разрядов нечетного цикла 30-го канала и параллельно в дешифратор 4 сигналов управления,Дешифратор 4 сигналов управления собран по той же схеме, что и дешифратор б адреса (фиг.4).Формирователь 5 коменд согласования скоростей (фиг.5) собран из восьми логических элементов 8 ИЛИ 61, 62, 67, 68, 71, 72, 76 и 77, двух логически элементов 4 ИЛИНЕ 69 и 70, двух триггеров 63 и 74, трех логических элементов ЗИ 64-66, логического элемента 2 ИЛИ - НЕ 73 и инвертора 75. Формирователь команд согласования скоростей управляется дешифратором 4 сигналов управления через коммутаторы 8 передачи. Дешифратором управления расшифровывается адрес канала для которого производится согласование, передается команда в соответствующий коммутатор передачи, в котором определяется вид согласования (положительное или отрицательное), и в формирователь команд согласования скоростей на соответствующий вход поступает положительный потенциал и инвертированный поступает на соответствующие установочные входы триггеров 63 и 74, которыми набираается соответствующая комбинация на трех схемах совпадения 64-66 для передачи в оборудование ИКМ на 6-8 разряды 30-го канала нечетного цикла. При поступлении сигнала положительного согласования на выходе сборки 70 (4 ИЛИ-НЕ) возникает нулевой потенциал,которым триггеры 63 и 74 устанавливаются в положение "1", схемы совпадения подготовлены к передаче комбинации 1 0 1, При поступлении сигнала отрицательного согласования нулевой потенциал возникает нэ сборке 69 (4 ИЛИ-НЕ), триггер 63 устанавливается в положение "0", а триггер 74-в положение "1", схемы совпадения подготовлены к передаче комбинации 0 1 О, Если ни на один вход сигнал согласования не поступил, то установившиеся положительные потенциалы на выходах сборок 63 и 74 поступят на схему совпадений 73 (2 И - НЕ), триггер 74 установится в положение "0", схемы совпадений 64-66 будут закрыты, в линию будет передаваться комбинация 0 0 О, Следует иметь в виду, что за один цикл на формирователь команд согласования скоростей может поступить только одна команда, что определяется формирователем адреса,Коммутатор 7 приема по числу каналов п редставляет собой (фиг, 2) восемь коммутационных цепей на схемах совпадения 2 И 11 и 12 и логики 2 ИЛИ - НЕ 13 каждая, В цепях управления стоят триггеры 26 и 27, логические элементы 2 И 23 и 24, 2 ИЛ И 25 и 2 ИЛ Ив НЕ 25, Коммутатор 7 приема работает следующим образом. На входы схем совпадений 11 подаются сигналы соответствующего канала, а на входы схем совпадения 12 - сигналы четного цикла 30-го канала, При отсутствии сигналов согласования скоростей нулевым потенциалом, поступающим от блока памяти, триггер 26 установлен в положение "1", а триггер 27 - в положение "0", подготовлены к коммутации схемами 11 совпадения цепи соответствующего основного канала, сигналы которого коммутируются в блок памяти, Припоступлении команды положительчого согласования по цепи "е" от дешифратора команд согласования скоростей триггер 27 устанавливается в положение "1", тем самым готовятся к коммутации цепи от дополнительного 30-го канала через схемы 12 совпадения и устанавливается в положение "0" триггер 26, закрывая цепи основного канала, Производится коммутация информации, поступившей по дополнительному каналу. При поступлении команды отрицательного согласования триггер 26 по цепи "б" от дешифратора команд согласования скоростей устанавливается в положение "0", триггер 27 также продолжае" оставаться в положении "0", все цепи коммутации блокируются, информация данного цикла .в блок памяти не коммутируется, так как на данных позициях соседняя станция ее не передавала. Цепи на логических элементах 23-25 служат для коммутации 8 импульса тактовой часто- ты коммутируемого канала для установки элементов определителя 3 заполнения блока памяти, блока 2 памяти и коммутатора 7 приема в исходное состояние,Блок 2 памяти представляет собой матрицу (фиг,. 2) из 24 ячеек-три столбца по восемь ячеек. Первый столбец состоит из восьми триггеров 14. второй - из восьмитриггеров 15 и третий - из восьми триггеров 16. В реверсивные установочные цепи первого и второго столбцов включены инверторы 19 и 20, При поступлении на первый столбец информация тактовым импульсом восьмого разряда принимаемого канала перезаписывается во второй столбец и в третий, если он свободен. Тактовый импульс поступает через определитель заполнения блока памяти по цепям "а" и "Ь" одновременно с перезаписью церез инверторы 19 и 20, которые выполняют также роль линий задержки, производится установка ячеек в исходное. положение. Передача из блока памяти ведется из третьего столбца,Схема коммутатора 8 передачи (фиг, 2) состоит из восьми схем совпадения ЗИ 17, восьми схем совпадения ЗИ 18, двух триггеров 30 и 31. в установочные цепи которых включены логические схемы 2 И - НЕ 28 и 29.во вспомогательные цепи включены логическая схема 2 ИЛИ - НЕ 21 и инвертор 22, Управление коммутатором передачи производится определителем заполнения блока памяти, Если блок памяти не переполняется и не опустошается, то триггер 30 находится в положении "1". а триггер 31 в положении "0", через схемы 17 совпадения ЗИ передача ведется по ось овному каналу, Если блок памяти начинает переполняться, то в коммутатор передачи поступает полокительный потенциал )т дешифрэтора сигналов управления и по цепи "г" от определителя заполнения блока памяти, которые через логическую схему 29 устанавливают триггер 31 в положение "1", создается цепь передачи информации по дополнительному каналу. Одновременно по цепи (+) подается положительный потенциал на формирователь команд согласования скоростей, откуда в тракт передается команда положительного согласования, При опустошении блока памяти в коммутатор передачи от дешифратора сигналов управления положительный потенциал поступает по цепи Т, в этом случае триггер 30 устанавливается в положение "0", триггер 31 также остается в положении "О". положительный потенциал на формиро атель команд согласования скоростей подается по цепи (-), откуда в тракт передается команда отрицательного согласования, цепи передачи коммутатора блокирую гся на один цикл - опустошение блока памяти компенсируется. Логическая схема 21 и инвертор 22 служат для коммутации импульса тактовой частоты восьмого разряда канала передачи в определитель запогнения блока памяти для установки его элементов в исходное со 20 25 формирователь адреса, При заполнении 30 35 40 и триггер 38, Если передача из блока памяти ведется несколько медленнее, чем прием, то наступит такой момент, когда ячейки всех трех столбцов будут заполнены. В этом случае все три триггера 33, 38 и 45 будут в положении "1", через схему ЗИ - НЕ 35 триггер 36 установится в положение "1", по цепи "ц" будет передан сигнал о положительном согласовании в коммутатор передачи, а по цепи "К-в формирователь адреса, Из блока памяти по дополнительному каналу будет передана очередная восьмибитовая пачка - переполнение будет устранено,Технико-экономическая эффективность предлагаемого усгроиства состоит в том, что оно позволяет производить согласование скоростей приема ипередачи при алек. 45 50 55 51015 стояние, одновременно выполняя роль линий задержки.Определитель 3 заполнения блока памяти состоит (фиг. 3) из пяти инверторов 32, 37, 43, 44 и 46, пяти триггеров 33, 36, 38, 42 и 45, двух логических схем ЗИ 34 и 39, двух логических схем ЗИ - Н Е 35 и 41 и логической схемы 2 ИЛИ - НЕ 40, Упоавляется от коммутатора приема по цепи "тчР 8 пр", от коммутатора передачи по цепи "тчР 8 пер", от дешифратора сигналов управления по цепи (см, чертеж), Работает следующим образом, Когда все ячейки блока памяти не имеют информации, триггеры 33, 38 и 45 окажутся в положении "0", так как из тракта приема очередная комбинация еще не поступила, следовательно, не прошел сигнал по цепи "тч Р 8 пр",а передача из последнего столбца уже произведена, сигнал "тч Р 8 пер" прошел через логическую схему ЗИ - НЕ, триггер 42 будет в положении "1", по цепи "Г будет передан сигнал об отрицательном согласовании в коммутатор передачи, а через логический элемент 2 ИЛИ-НЕ по цепи Ъ" в блока памяти после каждой принятой восьмибитовой комбинации в определитель заполнения по цепи "тч Р 8 пр" поступает импульс через инвертор 32 на триггер 33 и логицеские схемы 34 и 39, При передаче из блока памяти после каждой переданной восьмибитовой пачки в определитель заполнения по цепи "тч Р 8 пер" через инвертор 44 поступает импульс на реверсивный установочный вход триггера 45, который устанавливается в положение "0", готовится к перезаписи в третий столбец, цепь управления Т, Аналогичное действие производится при перезаписи из второгостолбца. В этом случае уцаствуют логическая схема 34 тронной коммутации каналов с импульсно-кодовой модуляцией, что дает возможность по оммутируемым сетям с1 а 1786671 Таблица 1 ТАБЛИЦА КОДИРОВАНИЯ КАНАЛОВ одолжение табл аблицв 2 ционвльнал таблица микросхемы К 155 ИВ ИКМ передавать не только аналоговую (разговор),но и дискретную информацию.Формула изобретения Ретранслятор асинхронных сигналов с им пул ьс но-кодовой модуля цией, содержащий дешифратор кома 11 д согласования скоростей, блок памяти, подключенный к двум его управляющим входам определитель заполнения блока памяти, дешифратор сигналов управления и формирователь команд согласования скоростей, о т л и ч а ю щ и йс я тем, что, с целью повышения пропускной способности, введены дешифратор адреса, коммутатор приема. коммутатор передачи и формирователь адреса, управляющий вход которого подключен к выходу определителя заполнения блока памяти, второй и третий выходы которого соединены с управляющими выходами коммутатора приема и коммутатора передачи, информационные входы последнего из которых через блок памяти соединены с выходами коммутатора приема, управляющие входы которого соединены с выходами дешифра тора команд согласования скоростей, к адресным входам которого подключены выходы дешифраторэ адреса, управляющий выход блока памяти соединен с управляющим входом коммутатора приема, другие 10 два выхода определителя заполнения блокапамяти подключены к адресным входам коммутатора передачи, управляющий вход которого обьединен с третьим входом определителя заполнения блока памяти и под ключен к выходу дешифратора сигналовуправления, адресные входы которбго подключены к выходам формирователя адреса, а формирователь команд согласования скоростей подключен к выходам коммутатора 20 передачи,

СмотретьЗаявка

4833415, 30.05.1990

ЦЕНТРАЛЬНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ СВЯЗИ

НЕВОЛИН НИКОЛАЙ СТЕПАНОВИЧ

МПК / Метки

МПК: H04J 3/00

Метки: асинхронных, импульсно-кодовой, модуляцией, ретранслятор, сигналов

Опубликовано: 07.01.1993

Код ссылки

<a href="https://patents.su/10-1786671-retranslyator-asinkhronnykh-signalov-s-impulsno-kodovojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией</a>

Предыдущий патент: Совместимая система стереофонического вещания

Следующий патент: Устройство автовыбора

Случайный патент: Устройство для закрепления винтовых ножей